Ведущий большие интегральные схемы

Когда говорят ?ведущий большие интегральные схемы?, многие сразу представляют себе кремниевые пластины с нанометровыми техпроцессами, что-то вроде флагманских процессоров Intel или Apple. Но в реальной индустрии, особенно в сегменте промышленной автоматизации и управления, где я чаще всего сталкиваюсь, это понятие куда шире и приземлённее. Речь идёт не просто о вычислительной мощности, а о создании ядра системы, которое должно десятилетиями работать в условиях вибрации, перепадов температур и электромагнитных помех. Частая ошибка — гнаться за самыми передовыми техпроцессами, забывая, что для контроллера доменной печи или насосной станции надёжность и долгий срок поставки компонентов часто важнее, чем паспортная частота. Сам видел, как проект вставал на полгода из-за того, что выбранная ?модная? БИС снялась с производства, а альтернативы не было.

От спецификации к кристаллу: где кроются подводные камни

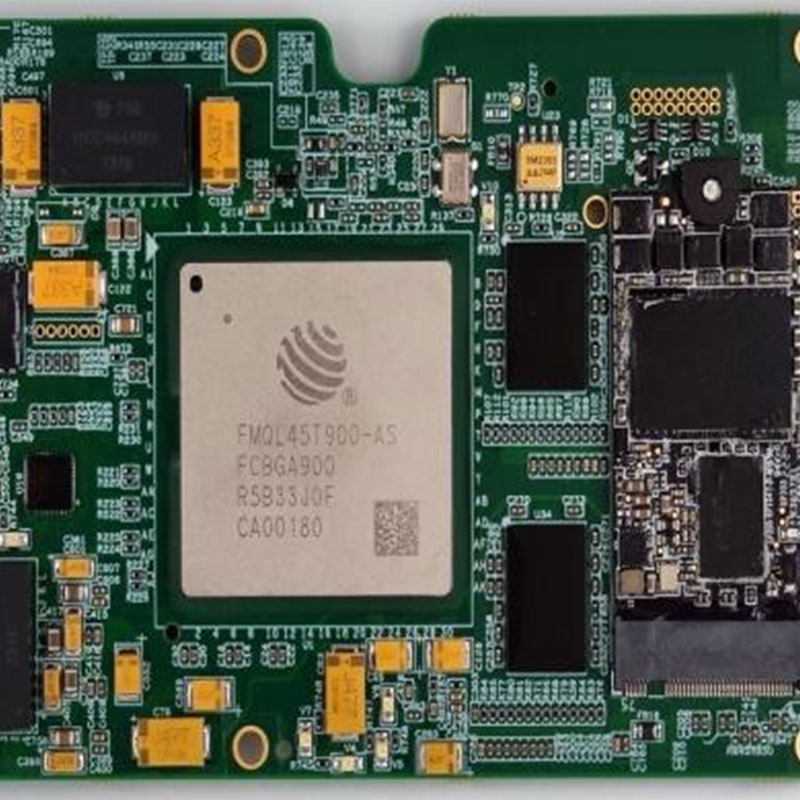

Начнём с начала. Получив ТЗ на систему, ты анализируешь, что можно взять готовым, а что требует кастомизации или разработки с нуля. Вот здесь и возникает вопрос о ведущей БИС. Иногда это может быть готовый микроконтроллер с ядром ARM, вокруг которого строится вся плата. Но в случаях, когда нужна специфическая обработка сигналов, работа с уникальными интерфейсами или жёсткие требования по энергопотреблению, без ASIC или сложного FPGA не обойтись. В ООО Шицзячжуан Чжунчжичуансинь Технологии мы как раз часто балансируем на этой грани: с одной стороны — готовые решения для быстрого выхода на рынок, с другой — разработка под конкретные задачи заказчика из области механического оборудования или силовой электроники.

Помню один проект по системе мониторинга для электромеханической сборки. Заказчик хотел анализировать виброакустический сигнал прямо на месте, в реальном времени, чтобы предсказывать поломки. Готовые процессоры не справлялись с алгоритмами без перегрева. Пришлось рассматривать вариант со специализированным сопроцессором — по сути, ведущей БИС для цифровой обработки сигналов, которую мы проектировали совместно с партнёрами. Ключевым был не только алгоритм, но и организация доступа к памяти, чтобы не было ?заторов?. Это та деталь, которую в учебниках не всегда разжёвывают.

И вот тут важный момент: выбор между FPGA и ASIC. FPGA — это быстро и гибко, можно вносить изменения хоть на лету. Но когда речь идёт о серии в десятки тысяч штук для управления промышленными компьютерами, цена за штуку и энергопотребление становятся критичными. Переход на ASIC — это всегда пари. Пари на то, что спецификация ?устоит?, что ошибки верификации будут минимальны, и что рынок не уйдёт в сторону, пока ты делаешь маску. Одна ошибка в RTL-коде, пропущенная на этапе симуляции, может привести к партии бракованных кристаллов. Убытки — колоссальные. Поэтому этап верификации — это святое, и он часто занимает больше времени, чем сама разработка архитектуры.

Взаимодействие с фабриками и реалии поставок

Допустим, архитектура утверждена, RTL проверен. Дальше — выбор фабрики и техпроцесса. 7 нм, 28 нм, 65 нм? Для промышленной электроники часто оптимальны ?зрелые? техпроцессы (например, 65-90 нм). Они дешевле, надёжнее, и фабрики не загружены под завязку заказами от гигантов вроде NVIDIA. Надо понимать, что ведущая БИС — это не только логика. Это ещё и аналоговые блоки: ФАПЧ, АЦП/ЦАП, блоки питания. Их проектирование — отдельное искусство, и они плохо масштабируются с уменьшением техпроцесса. Иногда аналоговая часть на 28 нм занимает больше площади и создаёт больше проблем, чем на 180 нм.

Сейчас, с этими геополитическими сложностями и разрывами цепочек поставок, вопрос выбора фабрики стал ещё острее. Нельзя положиться на единственного поставщика. Мы в своей практике всегда прорабатываем 2-3 возможных варианта производства, даже если это влечёт за собой дополнительные затраты на подготовку дизайна. Сайт zzcxkj.ru нашей компании отражает это направление деятельности — технический обмен и передача технологий, что в нынешних условиях означает в том числе поиск и адаптацию производственных решений под доступные мощности.

И ещё про сроки. Менеджеры любят спрашивать: ?Ну, когда кристаллы??. Стандартный цикл от отправки GDSII до первых инженерных образцов — это минимум 3-4 месяца. А потом ещё тестирование, доводка, возможно, вторая ревизия. Надо закладывать в планы не менее года. Многие стартапы этого не понимают и горят, не рассчитав время и бюджет. В промышленных проектах, где мы интегрируем такие схемы в системы продажи силовых электронных компонентов или коммуникационного оборудования, задержка в поставке чипа автоматически означает срыв контракта на поставку всей системы.

Системный уровень: чем ?болит? БИС после производства

Вот, получили первые образцы. Радуются все. Но это только начало истории. Чип — это не готовое устройство. Его нужно ?оживить? на печатной плате. И здесь начинается самое интересное: целостность сигналов, разводка питания, тепловой режим. Ведущая большая интегральная схема с тактовой частотой в гигагерцы — это мощный источник помех. Неправильная разводка земли может свести на нет все преимущества архитектуры.

Был у меня случай с платой для тестирования одной БИС, предназначенной для обработки видео в системах технического зрения. Чип работал, но периодически ?зависал?. Долго искали причину. Оказалось, проблема в помехах от DC-DC преобразователя, который питал ядро. На симуляции уровня системы этого не увидишь, только live-тестирование с осциллографом и анализом спектра помог. Пришлось переразводить плату, добавлять фильтры. Это к вопросу о том, что разработка БИС и разработка платы — должны идти рука об руку, с постоянной обратной связью.

И не забываем про программное обеспечение. Даже самый совершенный чип — просто кремний без драйверов, firmware, middleware. Часто команда софтверных инженеров начинает работу сильно позже, когда железо уже почти готово. Это ошибка. Архитектуру системы команд, организацию прерываний, доступ к периферии — всё это нужно проектировать совместно. В ООО Шицзячжуан Чжунчжичуансинь Технологии, где сфера деятельности включает и разработку программного обеспечения, мы стараемся выстраивать процесс так, чтобы ?железные? и ?софтверные? инженеры сидели в одной комнате (или хотя бы на одном Zoom-митинге) с самого начала проекта.

Экономика проекта: когда разработка БИС оправдана

Всё упирается в деньги. NRE (Non-Recurring Engineering) затраты на разработку и изготовление масок для ASIC могут достигать миллионов долларов. Поэтому ключевой вопрос: какой объём производства позволит отбить эти затраты? Для нишевых решений в области проектирования интегральных схем под конкретное механическое оборудование, тиражи могут быть не такими уж гигантскими — несколько десятков тысяч в год. Но если эта БИС позволяет заказчику сделать уникальный продукт, который захватит долю рынка, или резко снизить себестоимость своей конечной системы (например, за счёт замены платы с десятком микросхем на одну), то инвестиции окупаются.

Иногда выгода не только в деньгах. Например, в проектах для оборонки или критической инфраструктуры, где требуется максимальная надёжность и безопасность, собственная ведущая БИС, спроектированная по известным и контролируемым этапам, — это часто единственный приемлемый вариант. Здесь вступает в игру такое направление нашей работы, как техническое консультирование и передача технологий — помощь в оценке рисков и построении всей цепочки от идеи до серийного изделия.

Сейчас много говорят об открытых ядрах (RISC-V и других). Это, безусловно, снижает порог входа и даёт свободу. Но не стоит думать, что это панацея. Взять ядро — это полдела. Нужно его интегрировать в свою систему-на-кристалле, добавить периферию, проверить, что нет патентных конфликтов, обеспечить поддержку. Это всё равно большой и сложный проект. Но он действительно открывает новые возможности для среднего бизнеса, который хочет иметь контроль над ключевой технологией, не становясь при этом Intel.

Взгляд в будущее: что меняется в подходах

Раньше всё было более линейно: определили требования, спроектировали, отправили на фабрику, получили. Сейчас тренд — на гетерогенную интеграцию. Вместо того чтобы гнаться за нанометрами на всём кристалле, разные его части можно делать по разным техпроцессам (например, цифровое ядро — по 7 нм, а силовые драйверы — по 180 нм) и затем объединять в одном корпусе с помощью технологий типа SiP (System-in-Package). Это гибче и иногда экономичнее. Для сферы деятельности, указанной на zzcxkj.ru, например, для продажи промышленных управляющих компьютеров и систем, такой подход может быть ключевым для создания компактных и эффективных решений.

Ещё один момент — растущая роль специализированных ускорителей. Универсальные CPU/GPU хороши для широкого круга задач, но для ИИ на edge, для обработки радарных сигналов, для квантовой коррекции ошибок нужны свои, максимально заточенные под алгоритм, блоки. Будущее за гибридными архитектурами, где ведущая большая интегральная схема будет представлять собой платформу с набором таких ускорителей и гибкой системой их взаимодействия.

В итоге, возвращаясь к началу. Ведущая БИС — это не фетиш и не абстрактная ?мощность?. Это инструмент. Инструмент для решения конкретных инженерных и бизнес-задач: сделать устройство дешевле, надёжнее, компактнее или умнее. Её разработка — это всегда компромисс между производительностью, мощностью, стоимостью и временем выхода на рынок. И главное здесь — не слепо следовать трендам, а глубоко понимать потребности конечного применения, будь то система управления станком или новый коммуникационный модуль. Опыт, который набиваешь шишками на таких проектах, бесценен. И он точно не сводится к умению читать datasheet.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

LS3A5000

LS3A5000 -

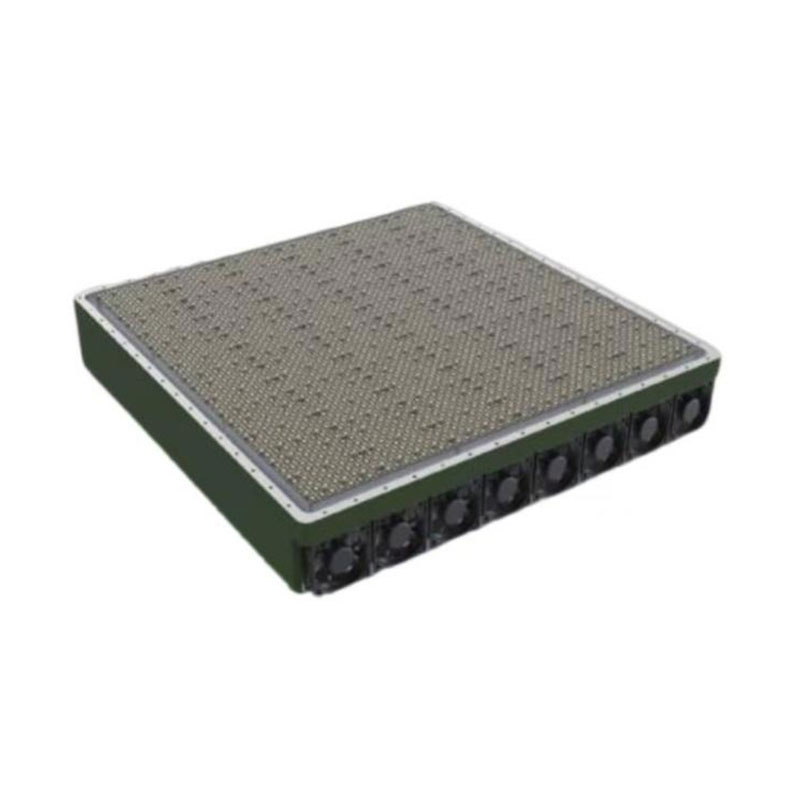

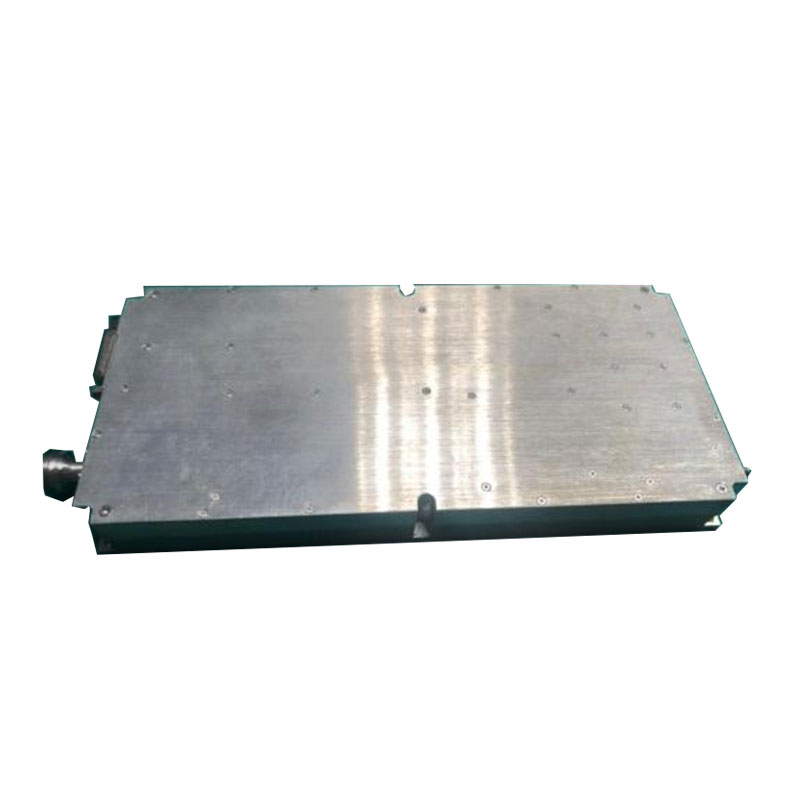

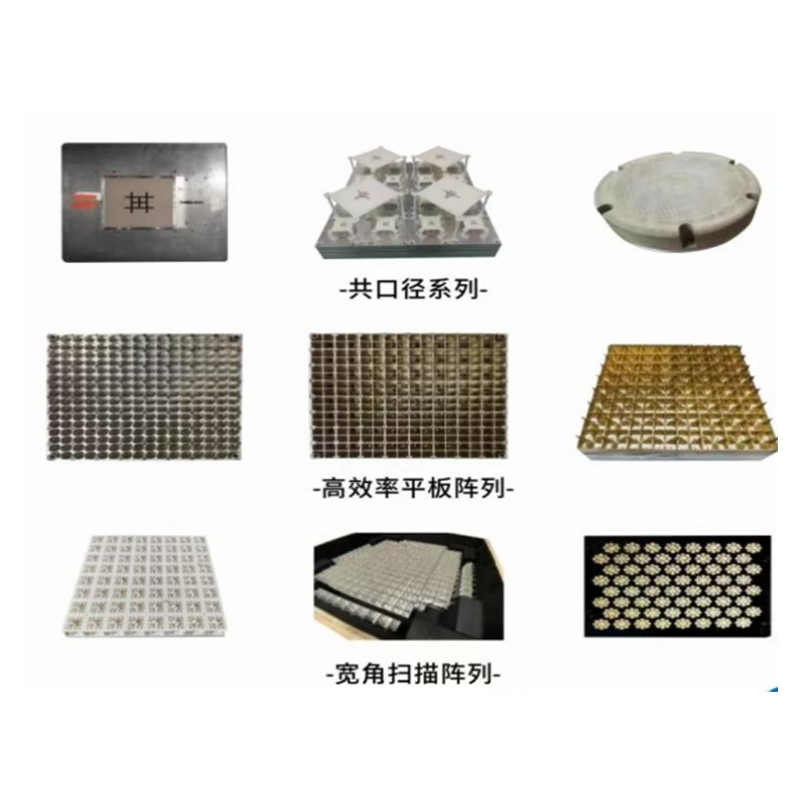

Метеорологический радар с фазово-резонансной TR-схемой

Метеорологический радар с фазово-резонансной TR-схемой -

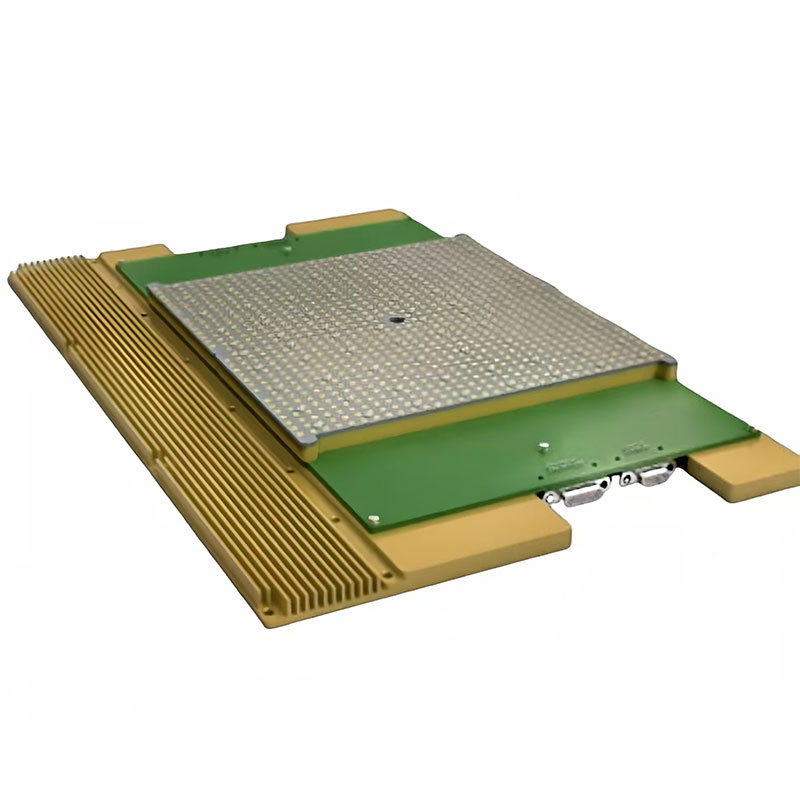

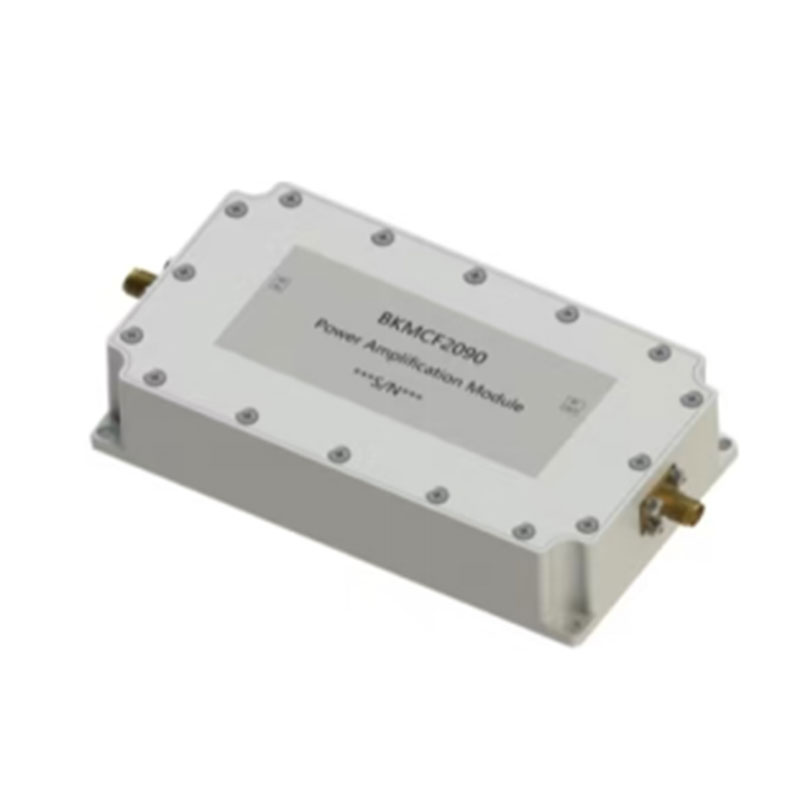

Модуль усилителя мощности (высокой мощности)

Модуль усилителя мощности (высокой мощности) -

STD3256M16

STD3256M16 -

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты -

D2000 COMe-ядро-модуль

D2000 COMe-ядро-модуль -

XAD7606

XAD7606 -

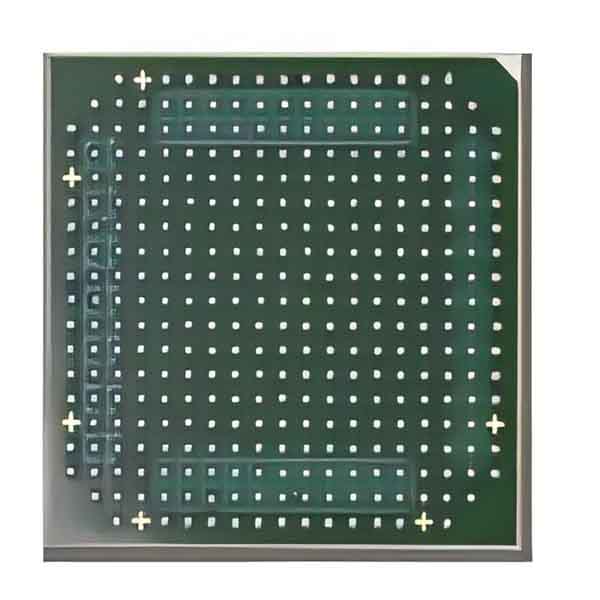

Модуль TR Kka с двухлучевой фазированной решеткой

Модуль TR Kka с двухлучевой фазированной решеткой -

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц -

LS3A6000

LS3A6000 -

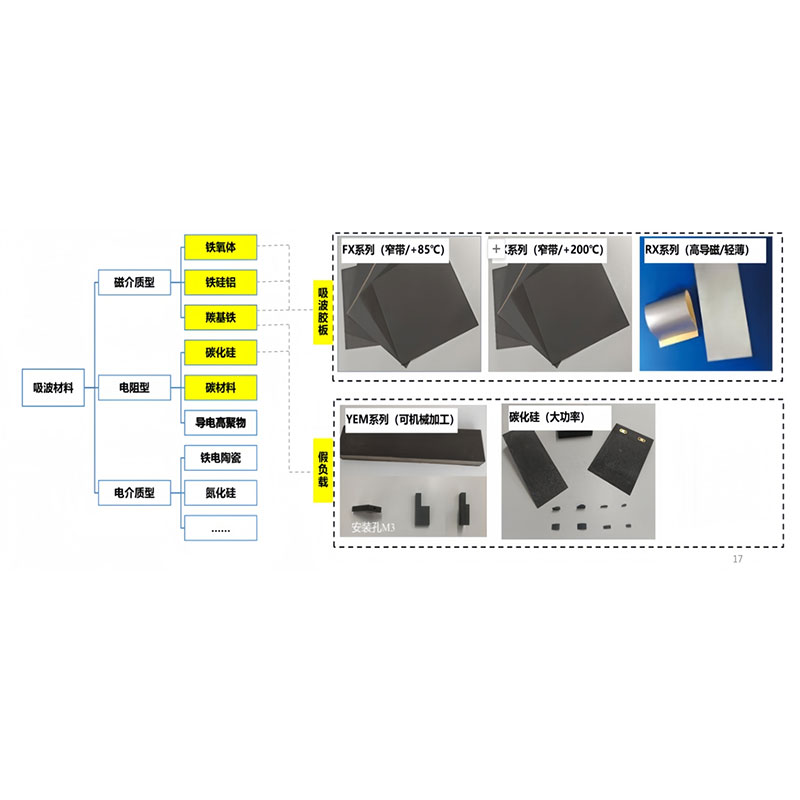

Радиопоглощающий материал

Радиопоглощающий материал -

UI32E103xCxE

UI32E103xCxE

Связанный поиск

Связанный поиск- Китай электронный преобразователь давления

- Высококачественный операционный усилитель

- Звуки микросхем производитель

- Ведущий основа интегральных схем производитель

- Плис (программируемая логическая интегральная схема) производители

- Китай электронный детектор поставщик

- Модуль питания ac-dc производители

- Китай центральный процессор цп производитель

- Китай фильтр-циркулятор поставщики

- Китай модуль питания dc-dc