Ведущий выводы микросхем

Когда говорят про ведущий выводы микросхем, многие сразу думают о трассировке в CAD, мол, развел дорожки — и дело сделано. На практике же это часто самая нервная точка перехода от ?виртуального? к ?железу?, где теоретические допущения сталкиваются с физикой производства, особенно если речь о плотных платах под промышленные контроллеры. Сам наступал на эти грабли не раз.

Не просто проводники: физика контакта и производственные допуски

Взять, к примеру, разработку плат для промышленных управляющих компьютеров. Здесь ведущий выводы микросхем — это не только электрическое соединение. Это вопрос теплоотвода, механической прочности паяного соединения и, что критично, технологичности монтажа. Помню случай с одним контроллером на базе ARM-процессора. В модели всё идеально: выводы микросхемы, ведущие к слоям питания, рассчитаны по току. Но на готовой плате при пиковой нагрузке начался перегрев в районе BGA-корпуса. Оказалось, переходные отверстия (via), которые должны были отводить ток и тепло вглубь платы, были слишком маленького диаметра для выбранного производителем процесса металлизации. Припой не заполнил их полностью, остались пустоты — сопротивление выросло, тепловой режим пошел вразнос.

Отсюда и важный нюанс: проектируя ведущий выводы, нужно заранее знать возможности и ?стандартные? параметры завода-изготовителя печатных плат. У одного — минимальный диаметр отверстия 0.2 мм, у другого — 0.3. Разница в 0.1 мм на высоких плотностях монтажа может решить, войдут ли все необходимые переходы под шариковую решетку или придется жертвовать целостностью земли. Это не пишут в учебниках по проектированию, это узнается через опыт или, увы, через брак.

Еще один момент — согласование импеданса. Для высокоскоростных линий, ведущих от выводов микросхем памяти или коммуникационных интерфейсов, это обязательно. Но часто в погоне за идеальной формой сигнала на симуляции забывают про резкие изгибы трасс под 90 градусов (хотя сейчас спорно, насколько это критично в цифровых схемах умеренных скоростей) или про длинные ?отростки? — стабы (stubs) на ответвлениях. Они становятся антеннами для помех. В проектах по передаче технологий, которыми, кстати, занимается ООО Шицзячжуан Чжунчжичуансинь Технологии, такие тонкости часто становятся предметом детального обсуждения, потому что напрямую влияют на надежность конечного устройства.

Программное обеспечение и ?железная? реальность: разрыв в ожиданиях

Инструменты САПР, те же Altium или KiCad, дают иллюзию полного контроля. Нарисовал контактную площадку (pad), провел от нее дорожку — и в 3D-визуализации всё красиво. Но файл Gerber, отправленный на завод, — это лишь набор инструкций для фотоплоттера и сверлильного станка. И здесь ключевое — как именно конструктор оформил сам вывод в посадочном месте (footprint).

Частая ошибка новичков — делать пады впритык к границам корпуса, особенно для компонентов с малым шагом выводов (например, QFN). В теории — экономит место. На практике — при малейшем смещении фотошаблона или если паяльная паста нанесена чуть смещенно, возникает риск короткого замыкания между выводами или, что хуже, образования мостика между выводом и открытой контактной площадкой-теплоотводом снизу корпуса. Приходится потом под микроскопом разгребать. Я всегда закладываю небольшой ?запас? по площади пада за пределами проекции вывода корпуса, особенно для ручной пайки или ремонта.

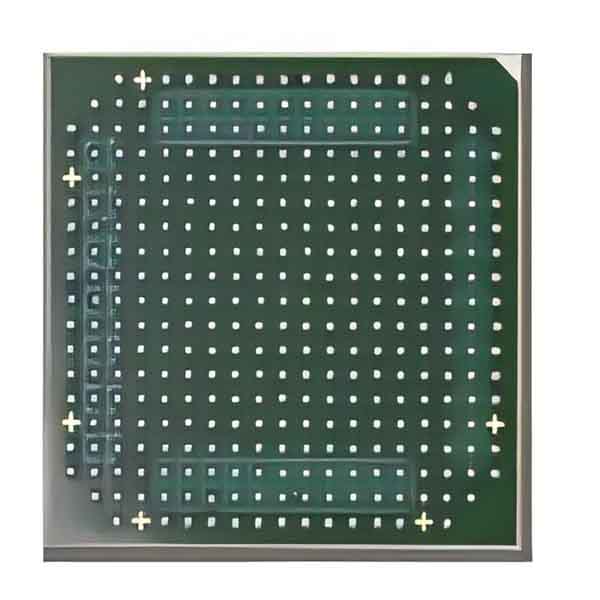

А еще есть сюрпризы от самих производителей микросхем. Даташит одного и того же чипа от разных партий или вторичных поставщиков может иметь микроскопические отличия в размерах корпуса. Не критично для DIP, но для корпусов типа LGA или мелкопитчного BGA это может привести к тому, что крайние шарики припоя лягут не на центр контактных площадок, а на их край. Надежность пайки падает. Поэтому для ответственных проектов, связанных с разработкой интегральных схем или их применением в силовой электронике, мы всегда запрашиваем у поставщиков не только даташит, но и рекомендации по посадочному месту (footprint recommendation), а иногда и 3D-модель для проверки в сборке.

Проваленный проект: когда выводы вели в никуда

Хочется рассказать про один неудачный опыт, который многому научил. Задача была сделать компактный драйвер для силовых электронных компонентов (IGBT). Плата двусторонняя, плотная, с смешанными сигналами: высокие токи и чувствительная аналоговая часть обратной связи. Чтобы сэкономить место, решили вести силовые дорожки с нижнего слоя на верхний через несколько сквозных отверстий прямо под корпусом микросхемы-драйвера. В симуляции цепей питания — всё в норме.

Но не учли паразитную индуктивность этих самых переходных отверстий. В момент быстрого переключения IGBT возникали всплески напряжения, которые через общие импедансы земли влияли на опорное напряжение аналоговой части микросхемы. На выходе — ложные срабатывания защиты, нестабильная работа. Плата в серию не пошла. Пришлось полностью переразводить, выделив отдельные, ?тихие? земли для аналоговой части и проведя силовые ведущий выводы строго по периметру платы, вдали от чувствительных узлов. Это был наглядный урок, что пути прохождения тока, особенно импульсного, нужно мысленно рисовать не только в редакторе, но и в голове, представляя реальные магнитные поля.

Именно такие кейсы, связанные с электромагнитной совместимостью (ЭМС) и целостностью сигнала, сейчас являются ядром многих технических консультаций. Компании, которые, как ООО Шицзячжуан Чжунчжичуансинь Технологии, занимаются техническим обменом и передачей технологий, часто выступают мостом между теоретическим проектированием и производственными реалиями, помогая избегать подобных тупиковых веток в разработке.

Взаимодействие с производством: диалог, а не просто отправка файлов

Пожалуй, главный вывод за годы работы: проектирование ведущий выводы микросхем — это не финальный этап работы инженера-схемотехника, а начало диалога с технологом производства. Перед отправкой любого проекта на изготовление, особенно когда речь идет о продаже готовых систем или аппаратных продуктов, необходимо согласовать производственный чертеж (assembly drawing).

На этом чертеже нужно явно указать, какие выводы критичны к положению, где допустим ручной ремонт, а где — нет. Например, для компонентов с шариковой решеткой (BGA) часто требуется указать обязательный контроль рентгеном. А для микросхем в корпусах QFN с открытой тепловой площадкой снизу — четко прописать требования к количеству и распределению паяльной пасты на этой площадке. Недостаток — плохой теплоотвод, избыток — чип может ?всплыть? на припое, и выводы не припаяются.

Сейчас многие сервисы предлагают проверку проекта на технологичность (DFM — Design for Manufacturability). Это полезно, но не отменяет необходимости лично понимать процессы. Зная, что на линии используется паяльная паста с частицами определенного размера (Type 3 или 4), можно заранее спроектировать ширину зазора между падами для мелкопитчвых компонентов так, чтобы не было слияния пасты. Это и есть та самая ?техническая услуга? в высоком смысле — не просто нарисовать, а спроектировать под конкретные условия.

Эволюция подхода: от ремесла к осознанной практике

Раньше многое делалось по аналогии или ?как в прошлом проекте?. Сейчас, с развитием средств симуляции (не только электрической, но и тепловой, и даже механических напряжений при перепадах температуры), подход становится более аналитическим. Можно заранее смоделировать, как будет течь ток по ведущий выводы силового ключа, и увидеть точки локального перегрева.

Но никакая симуляция не заменит ?щупания? проблемы руками. Всегда полезно иметь макет первой ревизии платы, чтобы под микроскопом посмотреть на пайку выводов, особенно по периметру корпусов. Иногда видишь, что припой не образовал нормального мениска на выводе, а лишь ?прилип? к боковой поверхности. Это сигнал, что либо пад слишком большой, либо профиль оплавления неоптимален.

В конечном счете, работа с ведущий выводы микросхем — это постоянный баланс между десятками требований: электрических, тепловых, механических, технологических и, конечно, экономических. Это не та область, где можно один раз выучить правила и следовать им всегда. Скорее, это набор эмпирических знаний и принципов, которые постоянно корректируются новыми материалами, компонентами и производственными процессами. И в этом, на мой взгляд, заключается главный интерес и вызов для инженера, будь то в области проектирования интегральных схем или создания конечных аппаратных решений.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

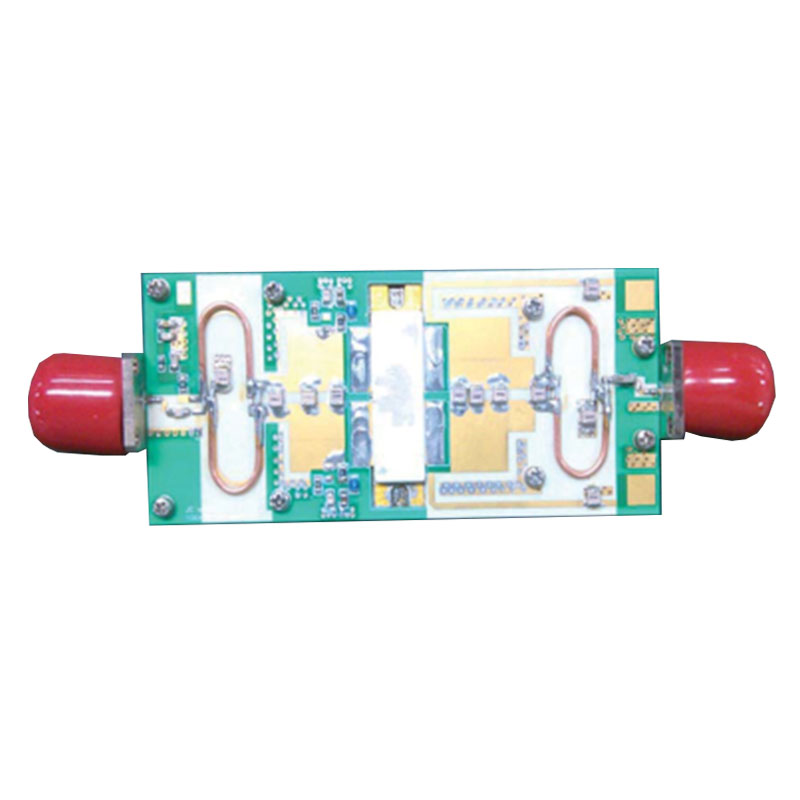

Усилители мощности ZPA1030M1090-1200 / ZPA960M1215-800

Усилители мощности ZPA1030M1090-1200 / ZPA960M1215-800 -

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц -

UI32E103xCxE

UI32E103xCxE -

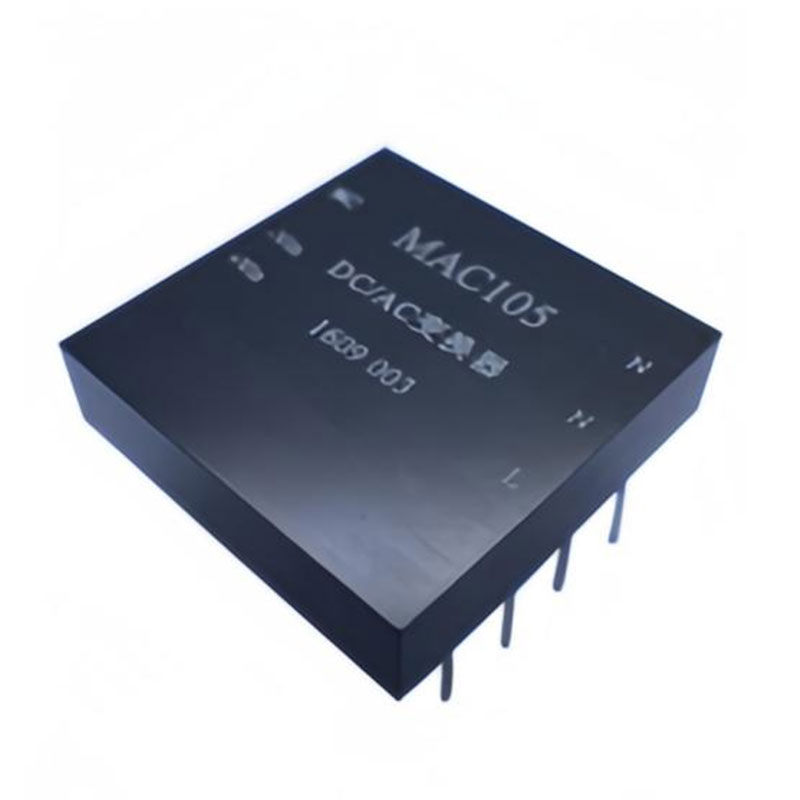

Силовой модуль M12S100AIR-GC

Силовой модуль M12S100AIR-GC -

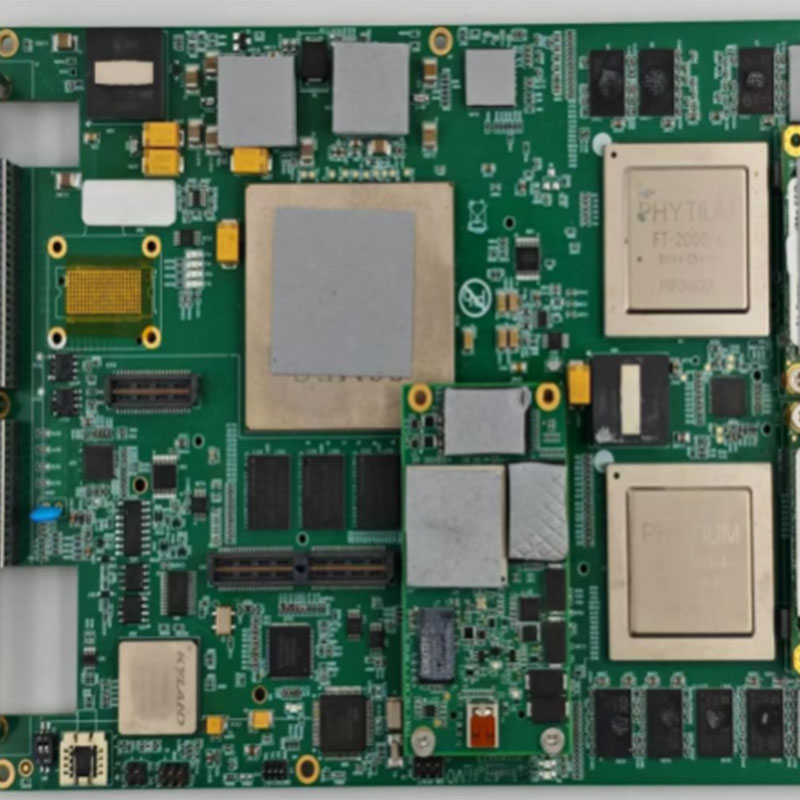

Многоканальный вычислительный модуль LRM

Многоканальный вычислительный модуль LRM -

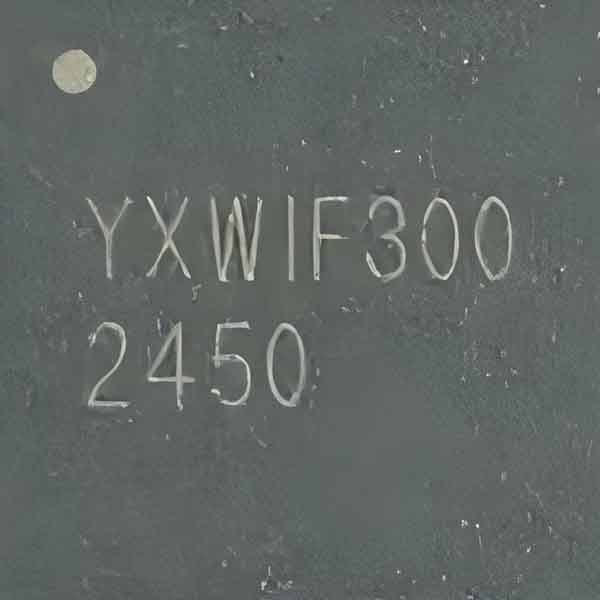

YXWIF300

YXWIF300 -

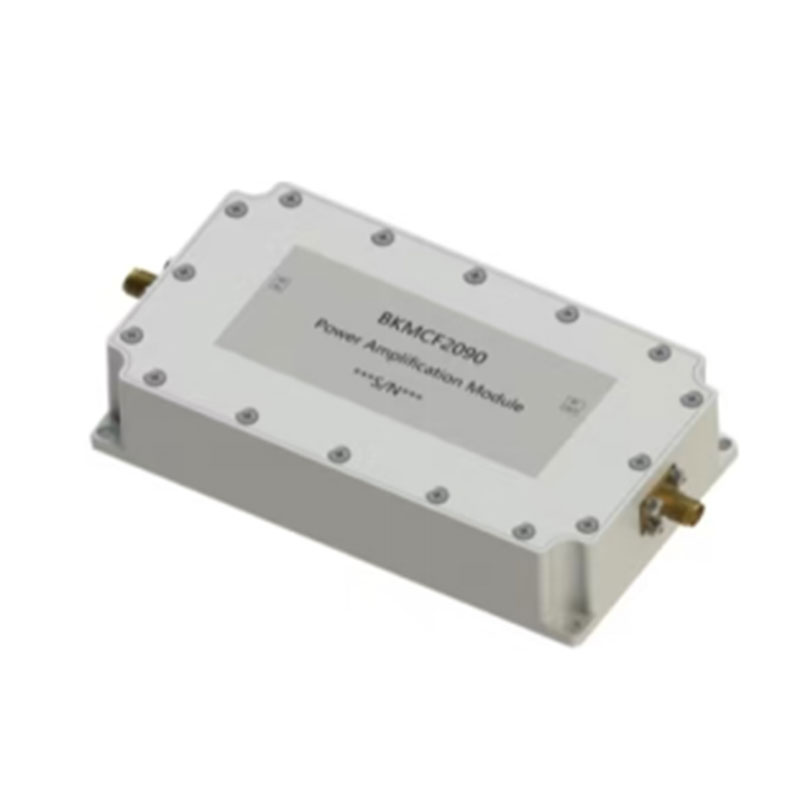

Модуль усилителя мощности (высокой мощности)

Модуль усилителя мощности (высокой мощности) -

Электронный трансформатор и индуктор

Электронный трансформатор и индуктор -

CWQ2P325T

CWQ2P325T -

Усилитель мощности — S-диапазон ZPA2700M3500-100

Усилитель мощности — S-диапазон ZPA2700M3500-100 -

HEG224A

HEG224A -

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты

Связанный поиск

Связанный поиск- Ведущий электронный блок преобразователя производители

- Центральный процессор

- Китай операционный усилитель звука поставщик

- Инвертирующий операционный усилитель поставщик

- Китай кристаллы интегральных схем поставщик

- Материал с фазовым переходом производитель

- Китай ммвч микросхема

- Китай электронное устройство задержки поставщики

- Китай модуль питания производитель

- Китай электронные компоненты интернет поставщик