Ведущий контроллер памяти

Если честно, когда слышишь ?ведущий контроллер памяти?, первое, что приходит в голову — это какой-то центральный узел, который всем управляет. Но на практике, особенно когда копаешься в отладочных логах или разбираешься с аномалиями пропускной способности, понимаешь, что это скорее дирижер, пытающийся сладить оркестр из разношерстных инструментов — разных типов памяти, шин, таймингов. И дирижер этот часто работает на пределе, компенсируя архитектурные несовершенства или бюджетные ограничения всей системы. Многие, особенно на старте проектов, недооценивают его роль, считая его задачу тривиальной — ?адрес подал, данные принял?. Пока не столкнешься с плавающими ошибками в условиях высокой нагрузки или необъяснимыми задержками при обращении к определенным банкам памяти. Вот тогда и начинается настоящее знакомство.

От спецификации к реальности: где кроется разрыв

Берем, к примеру, работу с промышленными управляющими компьютерами. Заказчик хочет надежность, предсказуемость временных характеристик. Ты открываешь datasheet на выбранный ведущий контроллер памяти, встроенный в SoC, и все выглядит прекрасно: поддержка DDR4, коррекция ошибок, прогнозируемые задержки. Начинаешь проектировать плату, разводишь линии по всем правилам длины, импеданса. Система собирается, POST проходит. И тут начинаются странности при длительном стресс-тесте с нашего собственного ПО для сбора данных. Не ошибки, а легкие ?проседания? пропускной способности раз в несколько часов. Логи контроллера, если, конечно, удается их вытащить (а это отдельная история), показывают периодические повторные калибровки. Оказывается, в погоне за энергоэффективностью контроллер слишком агрессивно управляет вольтажом и таймингами в зависимости от температуры кристалла, а наш тепловой режим в корпусе неидеален. Спецификация это не запрещала, но и не предупреждала. Пришлось лезть в регистры, вручную настраивать пороги, фактически отключая часть ?умных? функций. Так что ведущий — он не только исполняет, но и часто имеет свой, не всегда очевидный, ?разум?.

Еще один момент — интеграция с готовыми модулями. Мы как-то работали над проектом сбора данных с датчиков, где использовали готовый вычислительный модуль от другого вендора. Сам модуль — черный ящик, документация по его ведущему контроллеру памяти скудная. А нам нужно было добавить специализированный буферный чип SRAM для высокоскоростной временной привязки событий. Контроллер в SoC модуля формально поддерживал гибридные конфигурации, но попытка добавить внешний чип привела к тому, что тайминги основной DDR памяти ?поплыли?. Система то работала, то зависала. Пришлось методом тыка, анализируя осциллографом сигналы на шине адреса, подбирать такие настройки в регистрах задержек (write leveling, read gate training), чтобы оба устройства ужились. Ощущение, будто уговариваешь двух незнакомых людей танцевать один танец. И здесь никакая теория из учебников не помогает, только практика и иногда удача.

Или вот история, связанная с консультированием по одному проекту в области силовой электроники. Разработчики пытались использовать довольно мощный процессор с продвинутым многоканальным контроллером для управления преобразователями. Идея была в том, чтобы разные банки памяти обслуживали критичные по времени задачи управления ШИМ и фоновый логический анализ. На бумаге — отлично. Но они не учли арбитраж внутренней шины матрицы коммутации (Crossbar Switch). Когда оба ядра процессора одновременно обращались к разным физическим каналам памяти, возникали конфликты доступа, которые ведущий контроллер памяти разрешал с недетерминированными задержками. В силовой электронике такие задержки — это потенциальные сбои в синхронизации ключей и, как следствие, пробой. Решение оказалось на стыке hardware и software: пришлось перекраивать карту памяти, выделяя для критичных задач отдельный изолированный банк, и жестко привязывать задачи к ядрам ЦПУ, минимизируя конкуренцию за шину. Это был не столько недостаток контроллера, сколько просчет в системной архитектуре, где его возможности были использованы неграмотно.

Программная сторона медали: драйверы и прошивки

Часто вся сложность миграции на новую платформу упирается именно в инициализацию памяти. BIOS или U-Boot — это одно. Но когда пишешь или адаптируешь bare-metal прошивку для специализированного устройства, например, для того же промышленного контроллера, то сталкиваешься с нуля. Помню проект для одного стенда испытаний механического оборудования. Брали новый SoC. Первые две недели ушли только на то, чтобы заставить контроллер памяти стабильно работать в нашем режиме — не самом типовом, с mixed page size. Драйвер от производителя был как черный ящик, да и то для Linux. А нам нужна была минимальная инициализация для нашей RTOS. Пришлось по кусочкам реверсить последовательность инициализации из reference manual, которая занимала добрых 50 страниц. Ошибся в одном регистре при настройке фазы тактового сигнала (DLL phase) — и память молчит. Или, что хуже, работает нестабильно. Это кропотливая, почти ювелирная работа, где результат — это не красивые графики bandwidth, а просто стабильно работающий дампер памяти из отладчика.

Именно в таких нишевых проектах, где нет массового железа и готовых BSP, понимаешь ценность компаний, которые могут оказать глубокое техническое консультирование на этом уровне. Не просто продать плату, а помочь разобраться с низкоуровневыми особенностями. Я, например, знаю, что ребята из ООО Шицзячжуан Чжунчжичуансинь Технологии (сайт их — https://www.zzcxkj.ru) как раз заявляют в своей деятельности про техническое консультирование, обмен и передачу технологий в области интегральных схем и промышленных управляющих систем. Для инженера, который бьется над инициализацией ведущего контроллера памяти на новом для себя кристалле, такая экспертиза может сэкономить месяцы работы. Особенно если они сталкивались с конкретными линейками процессоров или имеют наработанные методики отладки. Их сфера, судя по описанию, довольно широка — от разработки софта до продажи электронных компонентов, что как раз намекает на системный подход, а не просто на торговлю железом.

Кстати, о софте. Современные контроллеры — это уже не просто набор регистров. У них есть встроенные процессоры (например, для того же training), свои микрокоды. Обновление микрокода (firmware для самого контроллера) иногда может кардинально улучшить стабильность работы с определенными модулями памяти. Но чтобы это обновление применить, нужно иметь доступ к закрытым утилитам от производителя SoC или к партнерским программам. Это создает дополнительную зависимость и сложность для небольших разработчиков. Получается, что выбирая платформу, ты выбираешь не только железо, но и экосистему доступа к таким инструментам. Иногда проще взять чуть менее производительный, но более ?открытый? или хорошо документированный контроллер.

Будущее: специализация и гибридные подходы

Сейчас тренд — это гетерогенные памяти. В одной системе могут быть и обычная DDR, и энергонезависимая память с памятью класса storage (SCM), и графическая HBM. Задача ведущего контроллера памяти усложняется до уровня менеджера гетерогенной памяти. Он должен не просто обеспечивать доступ, но и оптимально распределять данные между разными типами носителей по их характеристикам: скорость, latency, энергопотребление, стоимость бита. Это уже уровень интеллектуального управления, который требует тесной интеграции с операционной системой или гипервизором. Встраиваемые системы пока до этого массово не дошли, но в сегменте высокопроизводительных промышленных серверов или систем для ИИ это уже реальность. И здесь опять встает вопрос: будет ли этот интеллект ?жестко зашит? в контроллер, или он будет программируемым, позволяя адаптировать политики под конкретную нагрузку — например, под задачи анализа данных с датчиков в реальном времени.

В наших проектах мы пока сталкиваемся с этим лишь на этапе предпроектного анализа. Скажем, рассматриваем архитектуру для новой системы телеметрии. Нужно решить, стоит ли использовать отдельный быстрый буфер на основе MRAM или FeRAM для квитирования критичных пакетов, или можно обойтись выделенным регионом в обычной DDR с более сложной схемой кэширования на уровне контроллера. Решение упирается не только в стоимость, но и в то, насколько гибко можно запрограммировать логику работы контроллера, можно ли для этого буфера задать особые приоритеты доступа или гарантированную пропускную способность. Документация на контроллеры редко дает четкие ответы на такие вопросы, приходится делать предположения и проводить натурные эксперименты на демоплатах.

Именно в таких сложных, нестандартных сценариях становится ясно, что ведущий контроллер памяти перестает быть периферийным блоком. Он становится ключевым элементом, определяющим архитектурный облик всей системы, ее производительность, детерминизм и, в конечном счете, надежность. Его выбор и настройка — это не пункт в checklist при проектировании платы, а отдельная глубокая тема для исследований и переговоров с поставщиками платформ. И опыт здесь нарабатывается не чтением статей, а через подобные вот истории с плавающими ошибками, калибровками и долгими сеансами отладки по логическому анализатору.

Заключительные мысли: инженерный прагматизм

Так что, возвращаясь к началу. Ведущий контроллер памяти — это действительно дирижер. Но дирижер, который часто вынужден играть с расстроенными инструментами (неидеальными модулями памяти), в зале с плохой акустикой (неидеальной разводкой платы) и по партитуре, в которой есть неоднозначные места (неполная документация). Успех зависит от того, насколько хорошо ты, как инженер-дирижер, понимаешь не только его возможности, но и его ограничения, внутреннюю логику работы. Иногда лучшим решением является не гонка за самым навороченным контроллером с поддержкой последнего стандарта, а выбор более старого, простого и, главное, хорошо изученного тобой или твоим сообществом решения.

Работа с такими компаниями, как упомянутая ООО Шицзячжуан Чжунчжичуансинь Технологии, которые охватывают цепочку от проектирования и консультирования до поставки конечных компонентов и систем, может быть полезна как раз для сокращения этого пути накопления опыта. Их экспертиза, если она действительно глубока, может помочь избежать типовых ошибок при выборе и настройке платформы, сэкономив время и ресурсы. В конце концов, наша задача — не восхищаться сложностью ведущего контроллера памяти, а заставить его надежно и предсказуемо работать в конкретном устройстве, будь то промышленный компьютер или блок управления силовым приводом. И в этой задаче нет места абстракциям, только конкретные регистры, тайминги и осциллограммы.

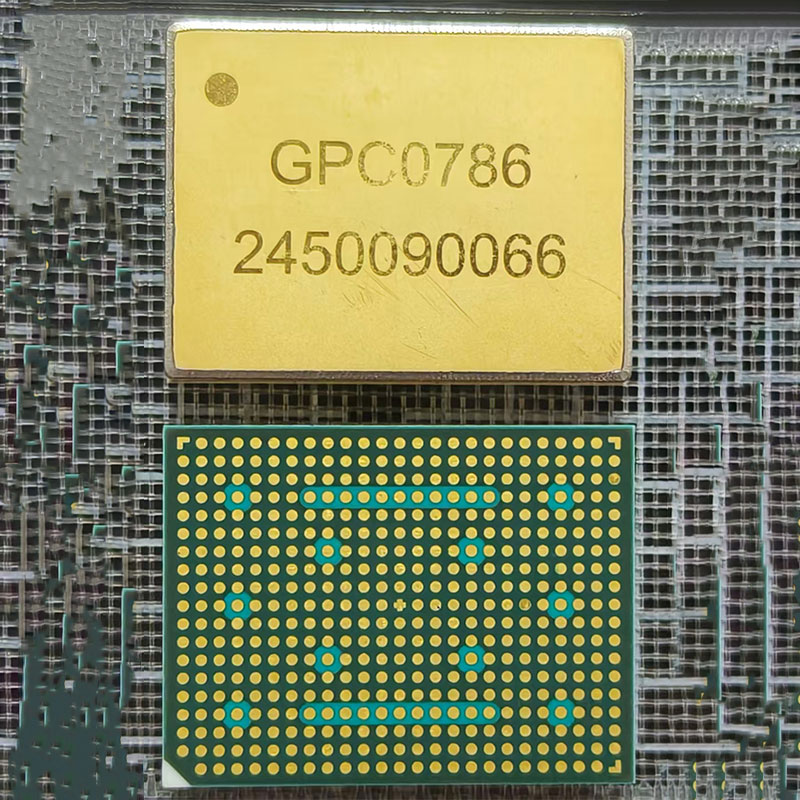

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продуктыСвязанный поиск

Связанный поиск- Китай проектирование интегральных схем поставщики

- Высококачественный микросхема памяти

- Ведущий электронный аттенюатор производитель

- Китай цифро-аналоговый преобразователь

- микросхема стабилизатор

- Китай цифровая микросхема производитель

- Китай центральный процессор цп

- Магнетрон поставщики

- Ведущий модуль питания ac-dc производители

- Ведущий электронный преобразователь частоты