Ведущий модуль центрального процессора

Когда говорят о ведущем модуле центрального процессора, многие сразу представляют себе некий центральный 'мозг', который всем управляет. Это, конечно, образно, но на практике вводит в заблуждение. Гораздо ближе к сути — роль дирижёра в оркестре, где каждый исполнитель (вычислительное ядро, кэш, контроллеры) знает свою партию, но без чёткого управления тактом и приоритетами начнётся какофония запросов к памяти и простои конвейеров. Именно этот 'дирижёрский пульт' и есть ведущий модуль. И его реализация — это не про абстрактные блок-схемы, а про ежедневную борьбу с латентностью, конфликтами шин и неожиданными 'узкими местами' в, казалось бы, продуманных системах.

От абстракции к кремнию: что на самом деле скрывается за термином

Если копнуть в микроархитектуру, скажем, современных серверных процессоров, то ведущий модуль — это часто даже не единый блок. Это распределённая логика, вшитая в подсистему когерентности памяти (чаще всего на основе протокола вроде MESI или его вариаций), в планировщики инструкций и в контроллер межсоединений. Его главная задача — обеспечить консистентность данных. Представьте: четыре ядра работают с одной областью памяти. Кто-то пишет, кто-то читает. Если не синхронизировать эти операции на аппаратном уровне, программа рухнет. Ведущий модуль отслеживает состояние каждой кэш-линии, разрешает конфликты, инвалидирует устаревшие данные в кэшах других ядер. Это титаническая работа, невидимая для программиста, но фундаментальная.

Вот на что часто не обращают внимания: эффективность этого модуля напрямую определяет реальную производительность многоядерной системы в 'неидеальных' условиях. Бенчмарки, работающие в пределах одного ядра или с идеально разделяемыми данными, его слабо нагружают. А вот реальная корпоративная CRM или система моделирования, где потоки постоянно соревнуются за общие ресурсы, — это его полигон. И здесь начинаются сюрпризы. Например, 'ложное разделение кэша' (false sharing), когда два независимых потока работают с разными переменными, но эти переменные попадают в одну кэш-линию. Ведущий модуль вынужден постоянно маркировать эту линию как модифицированную и синхронизировать её между ядрами, хотя данные-то разные! Производительность падает в разы, и искать причину без понимания работы этого модуля — как искать иголку в стоге сена.

Помню один проект по адаптации ПО для промышленного контроллера на базе многоядерного ARM. Заказчик жаловался на нелинейный рост производительности при добавлении потоков. Логировали всё, что можно, — бестолку. Пока не сели с логическим анализатором и не начали смотреть трафик на шине. Оказалось, алгоритм использовал общий массив счётчиков для статистики, и структура данных была выровнена крайне неудачно. Ведущий модуль процессора буквально 'захлёбывался', пытаясь поддерживать когерентность. Перепаковали структуру, выровняли по границам кэш-линий — проблема ушла. Это был наглядный урок: знание принципов работы ведущего модуля центрального процессора нужно не только проектировщикам CPU, но и тем, кто пишет для него софт.

Практические грабли: где теория расходится с реальностью железа

В документациях и белых книгах всё выглядит стройно: блок-схемы, конечные автоматы, временные диаграммы. Но когда начинаешь проектировать систему, особенно встраиваемую или промышленную, где нужно точно предсказывать время отклика, теория даёт сбой. Одна из главных проблем — недетерминированная латентность. Ведущий модуль, разрешая конфликты доступа, может вводить переменные задержки. В системах реального времени это смерти подобно.

Был у нас опыт с заказом на систему сбора данных с датчиков для 'умного' производства. Использовали, казалось бы, подходящий промышленный компьютер. Но в пиковые моменты, когда несколько каналов начинали одновременно требовать обработки и записи в общую память, возникали просадки по времени — 'джиттер'. Виновником оказался не сам CPU, а реализация протокола когерентности между его ядрами в конкретной SoC. Производитель сэкономил на ширине внутренней шины и буферах в ведущем модуле. При высокой нагрузке запросы становились в очередь, и время доступа 'плыло'. Пришлось менять архитектуру ПО, вводить локальные буферы на каждом ядре и снижать частоту взаимодействия. Жёсткий компромисс между производительностью и детерминизмом.

Это подводит к важному наблюдению: выбирая платформу для ответственных систем, нельзя слепо смотреть на гигагерцы и количество ядер. Нужно выпытывать у вендора или изучать самостоятельно детали реализации системной логики и когерентности. Иногда более 'медленный' по тактовой частоте процессор, но с продуманным и сбалансированным ведущим модулем, в реальной нагрузке окажется стабильнее и предсказуемее.

Связь с периферией: забытый фронт работы ведущего модуля

Часто обсуждение замыкается на взаимодействии ядер. Но не менее важна роль ведущего модуля в работе с периферией и внешней памятью. DMA-контроллеры, высокоскоростные сетевые карты, SSD-накопители — все они пишут и читают память, минуя ядра. И здесь ведущий модуль снова выступает арбитром. Он должен обеспечить, чтобы данные, записанные в память устройством DMA, стали немедленно 'видны' ядру, которое их обрабатывает. И наоборот — чтобы команды от ядра попали в контроллер вовремя, без риска потеряться из-за оптимизаций кэша.

В контексте компаний, которые занимаются интеграцией, вроде ООО Шицзячжуан Чжунчжичуансинь Технологии (сайт: https://www.zzcxkj.ru), это критически важно. Их сфера — продажа и интеграция промышленных управляющих компьютеров и систем. Клиенту, скажем, с автоматизированной линией, нужна гарантия, что данные с PLC или датчика изображения будут обработаны без задержек и потерь. Интегратор, зная нюансы работы ведущего модуля на выбранной платформе, может правильно настроить маршрутизацию прерываний, распределить области памяти для DMA и выбрать стратегию кэширования. Без этого знания система вроде бы соберётся, но будет работать на пределе надёжности, а в худшем случае — терять пакеты данных в самые ответственные моменты.

На их сайте указана деятельность, включающая техническое консультирование и передачу технологий. Вот как раз в этой области глубокое понимание системной архитектуры, включая роль ведущего модуля, и является той самой экспертизой, которую ждёт заказчик. Это не просто 'поставим компьютер поциклее'. Это способность объяснить, почему для задачи управления роботизированным комплексом лучше подойдёт плата с процессором, имеющим развитый IOMMU (Input–Output Memory Management Unit) — по сути, часть ведущей логики для периферии, — который изолирует и эффективно управляет доступом устройств к памяти.

Эволюция и будущее: от централизованного арбитра к смарт-фабрике

Раньше, в эпоху одно- и двухъядерных систем, ведущий модуль был относительно простым централизованным арбитром. Сейчас, с распространением гетерогенных вычислений (CPU + GPU, NPU, специализированные ускорители), его роль усложняется до невероятного. Речь идёт уже о целом 'согласующем слое' (coherency fabric), который обеспечивает единое адресное пространство и консистентность данных для десятков разнородных вычислительных элементов.

Это открывает новые возможности, но и новые проблемы. Например, в задачах машинного обучения на краю сети (edge AI), где нейросеть работает на связке CPU и встроенного NPU. Веса модели загружаются в память CPU, а затем NPU начинает их использовать. Если ведущий модуль не обеспечит строгую консистентность, ускоритель может начать работать с устаревшими или частично обновлёнными данными, что приведёт к ошибкам вывода. Проектировщики систем, такие как ООО Шицзячжуан Чжунчжичуансинь Технологии в рамках разработки интегральных схем или продажи силовых электронных компонентов, должны учитывать эти требования на уровне выбора компонентов и проектирования межсоединений.

Тренд будущего — ещё большее 'интеллектуализирование' этой подсистемы. Можно представить ведущий модуль, который не просто реагирует на конфликты, но и прогнозирует паттерны доступа, динамически меняя политики кэширования или приоритизации потоков данных на основе текущей нагрузки. Это уже не просто дирижёр, читающий партитуру, а импровизирующий маэстро, подстраивающийся под настроение оркестра. Но для этого нужны новые подходы к верификации и тестированию, потому что сложность системы растёт экспоненциально.

Заключительные мысли: почему это важно за рамками лабораторий

Так стоит ли инженеру-программисту или системному интегратору вникать в такие низкоуровневые детали? Мой опыт говорит — да, но с умом. Не нужно становиться экспертом по RTL-коду. Но понимать базовые принципы, знать типовые проблемы (вроде false sharing или contention на шине) и уметь читать соответствующие разделы документации на процессор — это must-have. Это знание превращается из академического в сугубо практическое в момент, когда оптимизация высокоуровневого кода перестаёт давать результат, а система должна работать быстрее или стабильнее.

Для компании, чья деятельность, как указано в описании ООО Шицзячжуан Чжунчжичуансинь Технологии, включает техническое развитие и продвижение технологий, такая экспертиза — это конкурентное преимущество. Возможность не просто собрать 'железо', а спроектировать систему, в которой все компоненты, от центрального процессора с его ведущим модулем до силовых электронных ключей, работают слаженно и предсказуемо. Именно это позволяет перейти от продажи оборудования к созданию комплексных решений, которые решают реальные бизнес-задачи клиента, будь то повышение точности станка или надёжности системы энергоснабжения.

В конечном счёте, ведущий модуль — это воплощение принципа 'дьявол кроется в деталях'. Можно годами работать в IT, не задумываясь о нём. Но когда возникает сложная, 'плавающая' проблема на стыке железа и софта, именно понимание этих деталей позволяет найти её корень, а не бороться со следствиями. Это и есть та самая профессиональная глубина, которая отличает исполнителя от эксперта.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

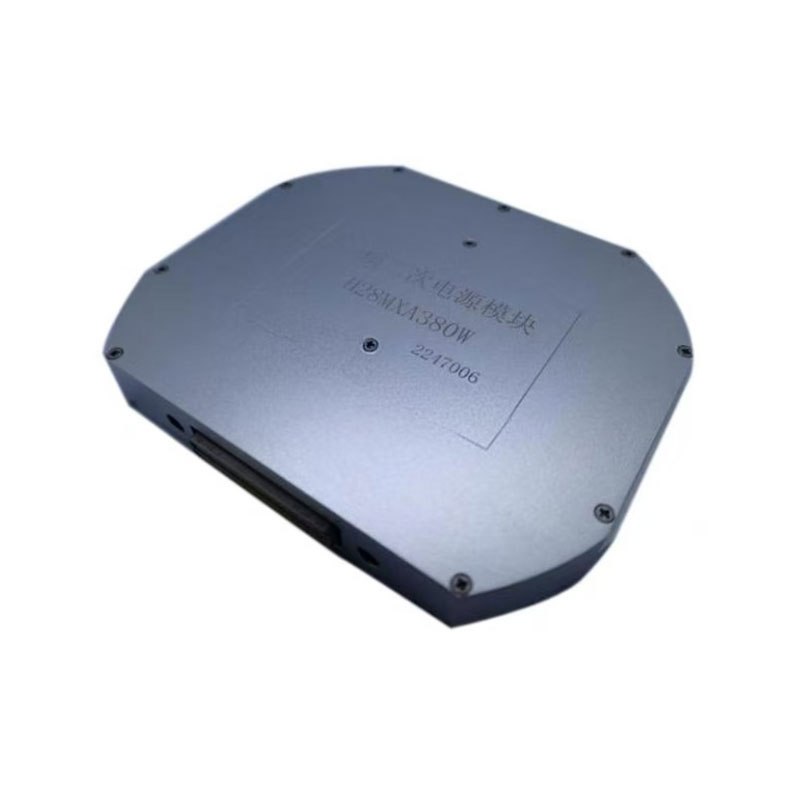

H28MXA380W

H28MXA380W -

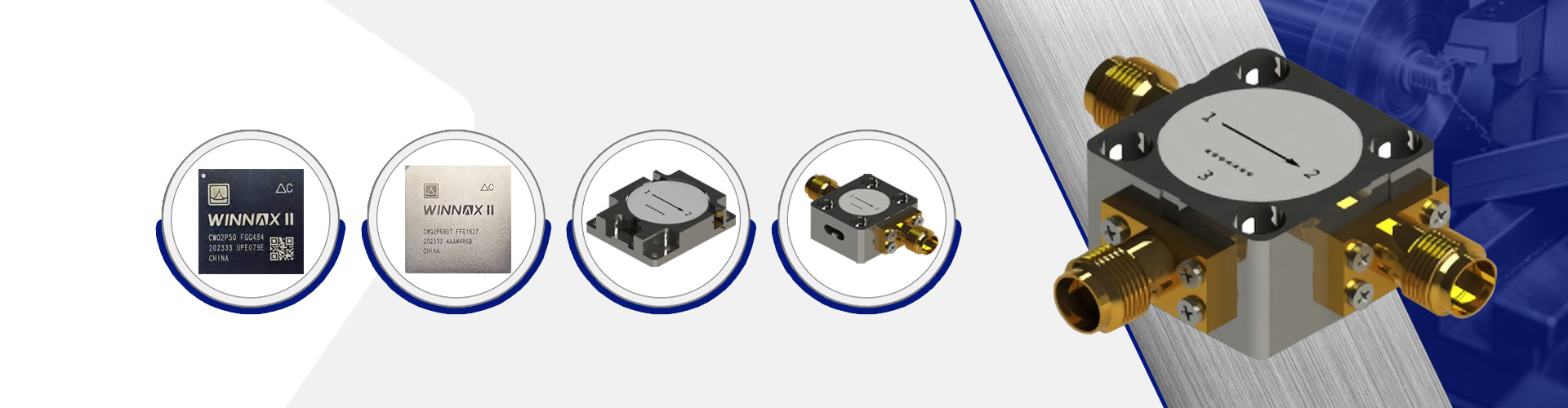

HEM388D-2

HEM388D-2 -

Мостовой чип Loongson 7A2000

Мостовой чип Loongson 7A2000 -

YX160023

YX160023 -

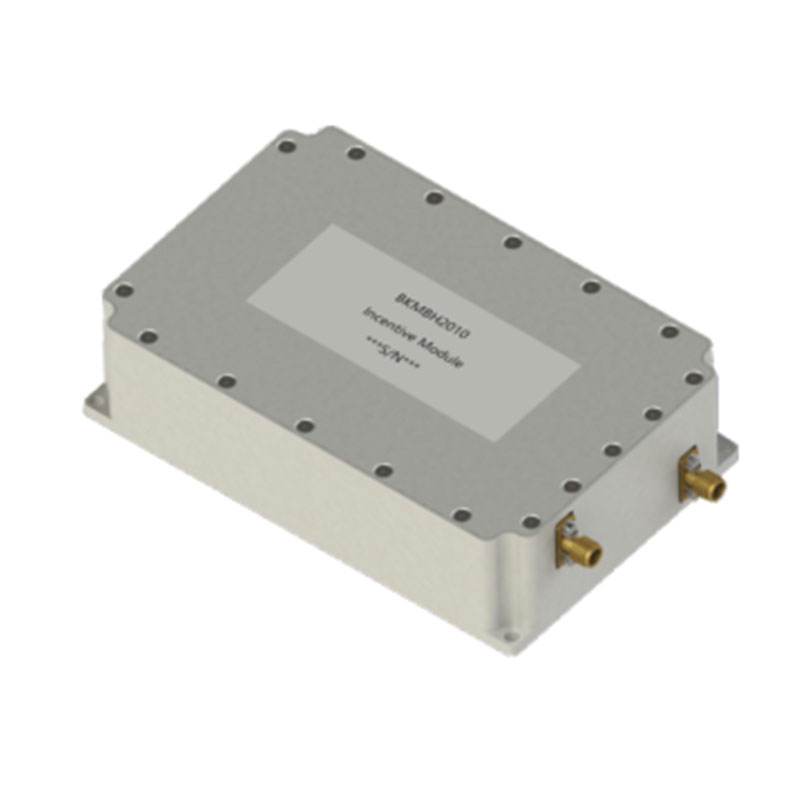

Усилитель мощности — S-диапазон ZPA2700M3500-100

Усилитель мощности — S-диапазон ZPA2700M3500-100 -

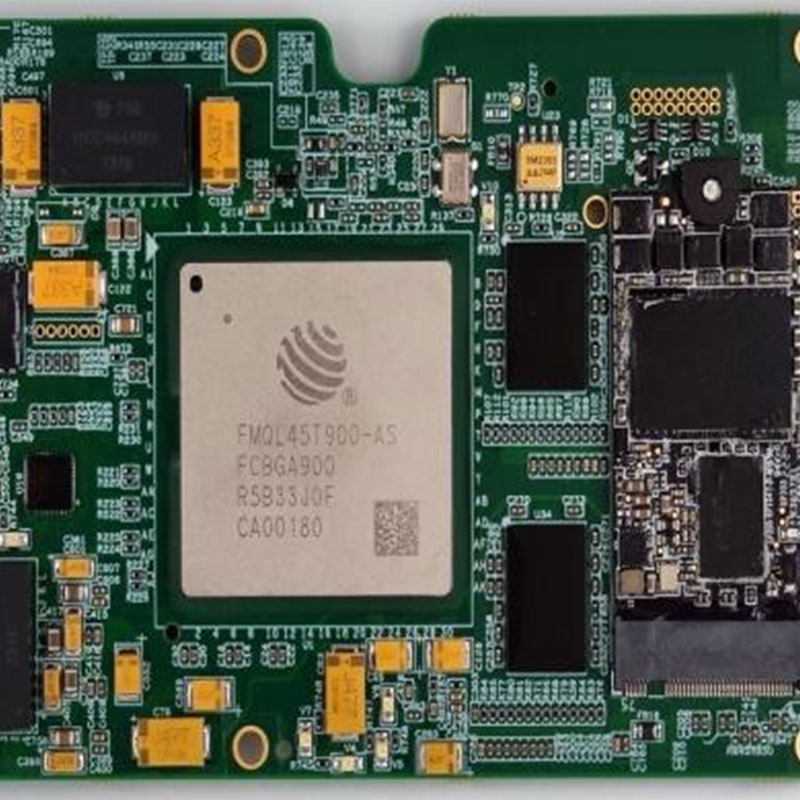

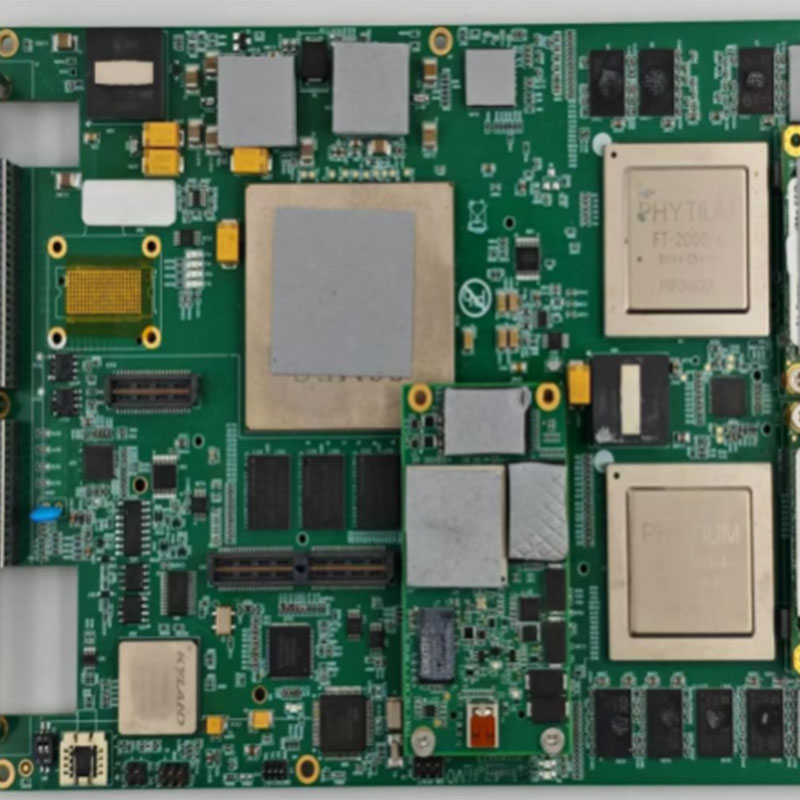

Многоканальный вычислительный модуль LRM

Многоканальный вычислительный модуль LRM -

Усилитель мощности ZPA2M30-1000

Усилитель мощности ZPA2M30-1000 -

YD14S2G5

YD14S2G5 -

Трехкомпонентный усилитель мощности X-диапазона

Трехкомпонентный усилитель мощности X-диапазона -

CWQ2P325T

CWQ2P325T -

Модуль TR Ku-диапазона, 16×16 стандартных фазированных подрешеток

Модуль TR Ku-диапазона, 16×16 стандартных фазированных подрешеток -

LS3A5000

LS3A5000

Связанный поиск

Связанный поиск- Китай кристаллы интегральных схем поставщик

- Китай микросхема производитель

- Ведущий фазированная антенная решётка

- Свч приёмопередающий модуль поставщик

- Ведущий проектирование интегральных схем производители

- Центральный процессор компьютера поставщик

- Китай цифровые интегральные схемы поставщики

- Микроконтроллер stm32 производители

- Электронный частотный преобразователь поставщик

- электронный блок преобразователя