Ведущий плис (программируемая логическая интегральная схема)

Когда слышишь ?ведущий плис?, первое, что приходит в голову — это какой-то главный, управляющий кристалл в системе. И вот здесь кроется первый, довольно распространённый, камень преткновения. Часто под этим подразумевают просто ПЛИС высокой степени интеграции или с мощными вычислительными ядрами. Но на практике, особенно в связке с промышленными управляющими компьютерами, ?ведущая? роль — это не только про гигатранзисторы, а про архитектурное решение, где программируемая логическая интегральная схема берёт на себя функции реального времени, оставляя CPU задачи более высокого уровня. Это тонкая грань, которую понимаешь только после нескольких проектов, где пытался всё запихнуть в микроконтроллер и получал нестабильные задержки.

Разбор понятия в контексте реальных задач

Если отбросить маркетинг, то ?ведущий? ПЛИС — это часто сердцевина custom-решения для специфических интерфейсов или обработки сигналов. Взять, к примеру, задачу агрегации данных с множества датчиков на производственной линии. Процессор может не справиться с потоком, если каждый канал требует строгой временной привязки. Здесь на помощь приходит ПЛИС: она выступает как интеллектуальный концентратор, выполняющий предварительную фильтрацию, упаковку данных и лишь затем передающий их по высокоскоростному интерфейсу (типа PCIe) основному вычислителю.

В нашей работе, связанной с разработкой и интеграцией систем, например, для таких компаний, как ООО Шицзячжуан Чжунчжичуансинь Технологии, которая занимается в том числе проектированием интегральных схем и продажей промышленных управляющих компьютеров, этот подход не теория. Их сфера — это как раз та область, где абстрактное проектирование сталкивается с ?железом?. Сайт https://www.zzcxkj.ru отражает широкий спектр деятельности — от передачи технологий до продажи силовых электронных компонентов. И именно в таких комплексных проектах роль правильно выбранной и запрограммированной программируемой логической интегральной схемы становится ключевой.

Ошибка, которую я часто наблюдал, — это попытка использовать ПЛИС как универсальный солдат. Берется кристалл с большим количеством логических ячеек, но без учёта требований к вводам-выводам, внутренней памяти или тактовым доменам. В итоге проект утыкается в ограничения по routing’у или потреблению, хотя ресурсов, казалось бы, ещё много. Выбор между семействами, скажем, Xilinx Kintex и Artix, или аналогами от Intel (Altera), — это всегда компромисс между стоимостью, энергопотреблением и необходимостью встроенных процессорных ядер Hard Core.

Практические сложности и ?подводные камни?

Один из самых болезненных уроков — это работа с тактовыми сигналами и доменами. В учебниках всё гладко, но когда проектируешь интерфейс для высокоскоростного АЦП или камеры, малейшая неточность в constraints-файле (файле временных ограничений) ведёт к нестабильной работе. Помню случай с разработкой платы сбора данных: ПЛИС должна была читать данные по LVDS. Сигнал приходил, но периодически возникали сбои. Долго искали проблему в схемотехнике, а оказалось — в неправильно описанном входном буфере в коде на HDL, плюс забыли задать false path для асинхронного сигнала сброса. Система вроде работала, но не в всех температурных диапазонах.

Другой аспект — это инструментарий. Vivado, Quartus — мощные среды, но их изучение отнимает месяцы. Автоматическая расстановка выводов (Pin Planning) иногда создаёт такие конфигурации, которые потом невозможно развести на плате без увеличения слоёв. Поэтому сейчас мы всегда начинаем с ручного планирования критических интерфейсов (DDR, Gigabit Ethernet), а уже потом доверяем автоматике второстепенные сигналы. Это та самая ?ручная работа?, которую не заменит никакой AI-ассистент в софте.

И конечно, верификация. Написание тестбенчей часто занимает больше времени, чем создание основного модуля. Особенно для сложных протоколов. Симуляция в ModelSim — это хорошо, но она не покажет всех проблем с целостностью сигналов на реальной плате. Поэтому следующий обязательный этап — это использование встроенных анализаторов (типа ChipScope или SignalTap), которые позволяют заглянуть внутрь работающего кристалла. Без этого этапа выход на https://www.zzcxkj.ru с готовым решением для интеграции информационных систем был бы просто авантюрой.

Интеграция в готовые системы и бизнес-составляющая

Когда ведущий плис спроектирован и отлажен, начинается этап его интеграции в конечный продукт. Здесь важно понимать экосистему. Например, если компания-заказчик, подобная ООО Шицзячжуан Чжунчжичуансинь Технологии, поставляет промышленные управляющие компьютеры, то наш модуль на ПЛИС должен бесшовно встраиваться в их стандартные шасси, соответствовать по питанию, охлаждению и иметь драйверы под нужные ОС (чаще всего Linux реального времени).

Это уже не только инженерия, а вопросы бизнес-процессов. Нужно ли лицензировать IP-ядро для Ethernet? Как быть с долгосрочной доступностью выбранной модели ПЛИС на рынке? Ведь производственный цикл изделия может быть 10 лет, а производители полупроводников обновляют линейки каждые 3-5. Приходится либо закладывать избыточный запас компонентов, либо сразу проектировать с оглядкой на pin-to-pin совместимость в рамках семейства.

Техническое консультирование, которое указано в деятельности компании, как раз часто касается этих вопросов. Клиенту нужно не просто ?железо?, а гарантия, что решение будет работать и поддерживаться годами. И здесь программируемая логическая интегральная схема даёт гибкость: при смене элементной базы можно мигрировать проект на новый кристалл, сохранив основную логику, и лишь адаптировать физический уровень.

Взгляд в будущее и место в технологическом стеке

Сейчас много говорят об FPGA в ускорителях ИИ и в центрах обработки данных. Это, безусловно, перспективно, но мой опыт подсказывает, что массовый спрос на ПЛИС останется именно в промышленности, телекоме, специализированной измерительной технике. Там, где нужна детерминированность, надёжность и возможность кастомизации под уникальные протоколы, которые ещё не стандартизированы.

Интересно наблюдать, как меняется подход к разработке. Раньше всё писалось на VHDL/Verilog вручную. Сейчас набирают популярность высокоуровневые синтез (HLS) и такие платформы, как Xilinx Vitis. Они позволяют перенести часть алгоритмов с C/C++ прямо в логику. Это мощный инструмент, но и здесь есть ловушка: автоматически сгенерированный код часто не оптимален по ресурсам и быстродействию. Для критичных по времени участков кода ручное описание на HDL пока вне конкуренции.

Таким образом, ?ведущий ПЛИС? — это не конкретная микросхема с полки, а концепция, роль в системе. Это результат выбора, компромиссов и глубокого понимания как аппаратной, так и программной части. Компании, которые, подобно ООО Шицзячжуан Чжунчжичуансинь Технологии, работают на стыке проектирования, технического обмена и поставки готовых решений, являются как раз теми интеграторами, которые превращают гибкость программируемой логической интегральной схемы в конкурентное преимущество для конечного заказчика. Успех определяется не мегагерцами или количеством LUT, а тем, насколько незаметно и безотказно работает это ?ведущее? звено в реальном, неидеальном мире.

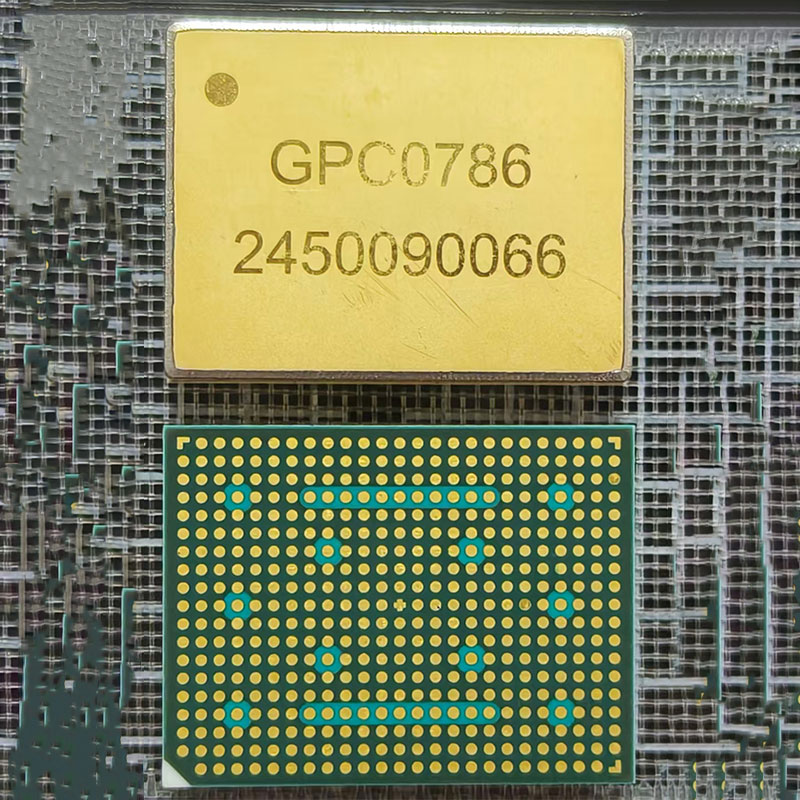

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продуктыСвязанный поиск

Связанный поиск- Китай электронные компоненты какие поставщики

- Большая интегральная схема эвм поставщики

- Китай производство электронных компонентов поставщики

- Электронные компоненты чипа производители

- Китай радиодетали и электронные компоненты

- Китай микросхема интерфейса производитель

- Ведущий подложка интегральной схемы

- Микросхема интерфейса поставщик

- Китай электронные интегральные схемы производители

- Аналоговые интегральные схемы поставщик