Ведущий проектирование интегральных схем поставщик

Когда слышишь 'ведущий проектирование интегральных схем поставщик', многие сразу представляют крупную фирму, которая просто поставляет готовые кремниевые пластины. Но это, пожалуй, самое большое заблуждение. На деле, если ты действительно в этой сфере, то понимаешь, что ключевое слово здесь — 'проектирование'. Это не про склад и логистику, это про то, чтобы взять сырую идею заказчика, часто смутную, и превратить её в работающую схему, учитывая кучу нюансов: от техпроцесса и библиотек элементов до сроков и, что критично, бюджета. Поставка железа — это уже финальный, пусть и важный, этап. Основная драма разворачивается гораздо раньше.

От спецификации до GDSII: где кроются подводные камни

Вот, к примеру, классическая история. Приходит клиент с блестящими глазами и ТЗ на что-то энергоэффективное для IoT. Спецификации вроде бы есть, но как начинаешь копать... Допустим, они хотят ультра-низкое энергопотребление в sleep mode. Казалось бы, берём библиотеки с низким leakage. Но тут же встаёт вопрос по аналоговой части, скажем, по АЦП или генератору тактовой частоты. Эти блоки в глубоком сне могут вести себя непредсказуемо, их вывод из сна требует времени и энергии. И вот уже первоначальная архитектура трещит по швам.

Часто проблема даже не в чистой схемотехнике, а в верификации. Моделирование на этапе RTL — это одно, а post-layout simulation с учётом паразитов — совсем другое. Помню один проект под 28 нм, где из-за неидеального размещения clock tree в одном углу чипа возникли серьёзные skews, которые на этапе синтеза не были видны. Пришлось экстренно переразмещать блоки, что съело две недели и, естественно, деньги. Это тот момент, когда понимаешь, что ведущий проектирование интегральных схем поставщик должен иметь не просто команду дизайнеров, а полноценный цикл инструментов для физической верификации и команду, которая умеет ими пользоваться в сжатые сроки.

Или взять выбор фабрики. TSMC, GlobalFoundries, SMIC — у каждой свои правила оформления данных, свои особенности техпроцессов. Решение, которое отлично работает на 40 нм одной фабрики, может потребовать значительной переработки для 55 нм другой, даже если цифра 'крупнее'. Всё упирается в доступные библиотеки стандартных ячеек, IP-блоки (те же PLL, SerDes) и, конечно, стоимость масочного комплекта. Иногда выгоднее использовать более 'старый' процесс, но с более отработанными и дешёвыми библиотеками.

Связующее звено: почему одни инженеры — это мало

Здесь мы подходим к главному. Хороший поставщик — это не просто пул талантливых инженеров. Это, прежде всего, грамотный проектный менеджмент и чёткие процессы. Нужен человек (или команда), который говорит на одном языке с заказчиком-системщиком и при этом может донести все ограничения и возможности до команды физических дизайнеров. Пропасть между системным уровнем и уровнем транзистора огромна.

Например, заказчик требует реализовать сложный алгоритм обработки сигнала. Алгоритмисты дают модель на MATLAB, всё работает идеально. Но когда начинаешь оценивать это в кремнии, выясняется, что предлагаемая архитектура потребует такого количества умножителей-аккумуляторов, что площадь чипа взлетает до небес. И вот тут начинается настоящая работа: совместный поиск архитектурных компромиссов. Может, часть вычислений можно сделать с меньшей разрядностью? Или перенести на более простой, последовательный процессор? Это постоянный trade-off между производительностью, площадью и энергопотреблением.

Именно в таких ситуациях важна экспертиза в смежных областях. Допустим, проект — это управляющий контроллер для промышленного оборудования. Чип спроектирован, но его же нужно впаять в плату, обеспечить стабильное питание, отвод тепла, защиту от помех. Понимание всего цикла — от проектирование интегральных схем до конечного монтажа — критически важно. Иначе может получиться так: чип в симуляции работает, на тестовом кристалле — тоже, а в реальном устройстве начинает глючить из-за наводок от силовых ключей. Поэтому в идеале поставщик должен иметь компетенции или надёжных партнёров и в области проектирования печатных плат, и в системной интеграции.

Кейс: интеграция в промышленные системы

Возьмём конкретную область — промышленные управляющие компьютеры. Здесь требования жёсткие: надёжность, работа в расширенном температурном диапазоне, долгосрочная доступность компонентов. Спроектировать специализированную ASIC для такой системы — это вызов. Нужно закладывать дополнительные цепи мониторинга (температуры, напряжения), возможно, избыточность критичных блоков. А ещё — обеспечить долгую поддержку. Фабрика может через 5 лет закрыть техпроцесс, и нужно иметь план миграции дизайна на новую линию.

В этом контексте интересно выглядит компания ООО Шицзячжуан Чжунчжичуансинь Технологии. Судя по описанию на их сайте https://www.zzcxkj.ru, их сфера — это широкий спектр от технического консультирования и передачи технологий до продажи промышленных управляющих компьютеров и силовых электронных компонентов. Такая вертикаль как раз намекает на потенциальное понимание полного цикла. Если они позиционируют себя в проектирование интегральных схем, то логично предположить, что их ценность может заключаться в способности не только нарисовать схему, но и понять, как этот чип будет работать в конечном изделии — том же промышленном компьютере или системе электромеханической сборки, которые они также упоминают. Это правильный, системный подход. Хотя, конечно, на бумаге всё выглядит гладко, а реальная экспертиза проверяется только в конкретных проектах.

Экономика проекта: когда NRE убивает идею

Говорить о техпроцессах и архитектуре — это одно. Но фундаментом любого проекта является его экономика. NRE (Non-Recurring Engineering) затраты — это та самая сумма, которую нужно заплатить за проектирование, верификацию и изготовление масок. Для современных норм ниже 16 нм это могут быть миллионы долларов. И это ещё без учёта стоимости самих кристаллов.

Поэтому ведущий поставщик часто начинает разговор не с технологий, а с объёмов. Планируемый тираж в 10 тысяч штук? Тогда, возможно, нет смысла городить полноценную ASIC. Лучше взять готовый FPGA или даже микроконтроллер с периферией. А если речь о десятках или сотнях тысяч — тогда уже можно считать окупаемость NRE. Здесь нужна честность. Бывает больно объяснять клиенту, что его гениальная идея, увы, экономически нежизнеспособна в виде отдельного чипа. Но это часть работы.

Иногда выходом становится использование платформ типа SLM (Structured Logic Mask) или уже частично подготовленных базовых кристаллов, куда можно встроить свой IP. Это снижает NRE и время выхода на рынок. Но накладывает свои архитектурные ограничения. Опять trade-off. Умение найти оптимальный баланс между кастомным дизайном и полуготовыми решениями — это маркер зрелости поставщика.

Программная составляющая: прошивка, драйверы, SDK

Чип — это просто кусок кремния без программного обеспечения. И часто успех проекта зависит от того, насколько легко программистам с ним работать. Значит, в обязанности поставщика входит не только отдать GDSII файл на фабрику, но и подготовить хотя бы базовый набор инструментов для разработчика: описание регистров, заготовки драйверов, примеры кода для основных функций.

Особенно это критично, когда проектируется система-на-кристалле (SoC) с процессорным ядром. Нужно обеспечить портирование операционной системы (например, FreeRTOS или Linux BSP), отладить загрузчик. Я видел проекты, где аппаратная часть была сделана блестяще, но проект провалился из-за сырого и недокументированного программного стека. Клиент просто не смог начать разработку своего ПО в разумные сроки.

Поэтому сейчас многие компании, занимающиеся проектированием, обязательно имеют в штате или тесно сотрудничают с командами embedded-программистов. Это стало неотъемлемой частью цикла. Упомянутая ранее ООО Шицзячжуан Чжунчжичуансинь Технологии в своей деятельности указывает разработку программного обеспечения. Если это не просто формальная строчка, а реальная практика, то это серьёзное конкурентное преимущество. Возможность предложить клиенту 'под ключ' не только железо, но и софтовую начинку, резко снижает порог входа для него и повышает шансы на успех всего изделия.

Вместо заключения: что искать в партнёре

Так кого же можно считать тем самым ведущим проектирование интегральных схем поставщиком? На мой взгляд, это не обязательно гигант вроде Cadence или Synopsys (они больше про инструменты). Это организация, которая способна провести идею через весь тернистый путь: от концепции и экономического обоснования, через все этапы дизайна и верификации, выбор фабрики и изготовление прототипов, до поставки партии чипов и обеспечения её базовой программной поддержкой.

Их экспертиза должна быть глубже, чем знание скриптов для Cadence Innovus. Она должна включать понимание системного уровня, знание рынка готовых компонентов (чтобы не изобретать велосипед), опыт взаимодействия с фабриками и, что очень важно, прозрачные процессы коммуникации с заказчиком. Потому что 80% проблем рождаются из-за недопонимания на ранних этапах.

Поэтому, когда видишь компанию, которая заявляет о проектировании интегральных схем в одном ряду с техническим консультированием, передачей технологий и продажей конечных систем, как zzcxkj.ru, это вызывает определённый интерес. Потенциал для создания сквозного решения есть. Но, как и всегда в нашем деле, истина проверяется не списком услуг на сайте, а успешно сданными проектами и отзывами реальных заказчиков, прошедших весь этот сложный, но невероятно интересный путь от идеи до кремния.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

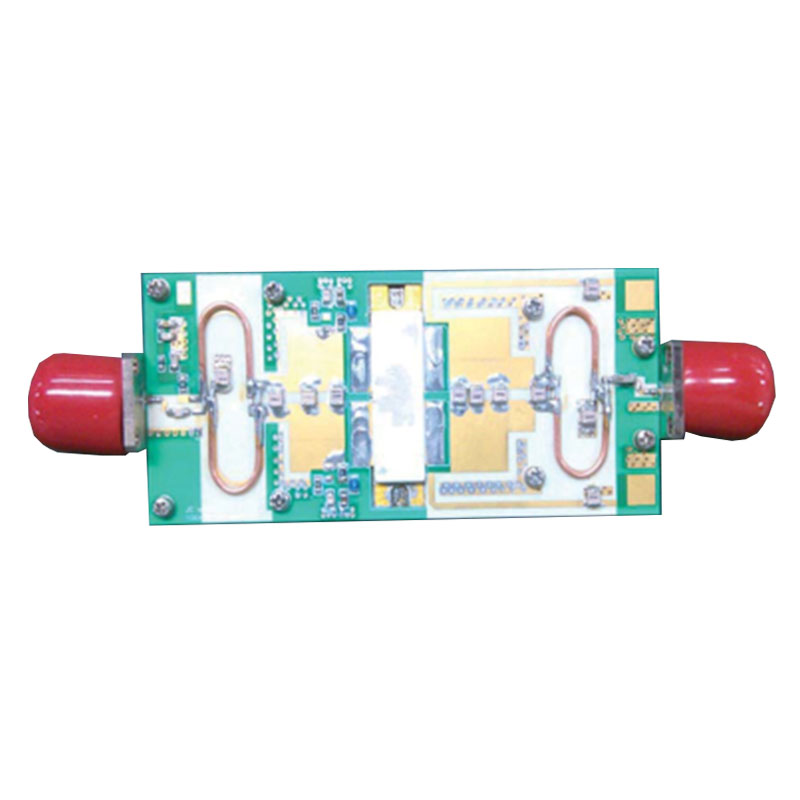

Усилители мощности ZPA1030M1090-1200 / ZPA960M1215-800

Усилители мощности ZPA1030M1090-1200 / ZPA960M1215-800 -

Интегральный микроконтроллер Loongson 1C203

Интегральный микроконтроллер Loongson 1C203 -

Трехкомпонентный усилитель мощности X-диапазона

Трехкомпонентный усилитель мощности X-диапазона -

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц

Компонент широкополосного фазированного приемника 1,1,6 ГГц ~ 8,4 ГГц -

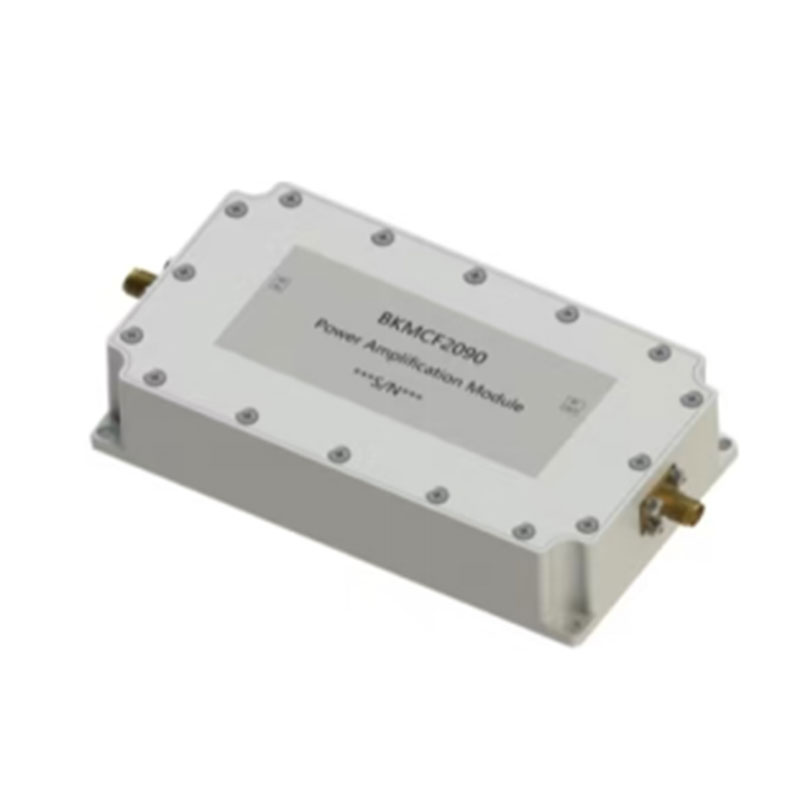

Модуль усилителя мощности (высокой мощности)

Модуль усилителя мощности (высокой мощности) -

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты

Серия SIPFC-CB-0026X — двухканальный модуль приёмо-передающего преобразования частоты -

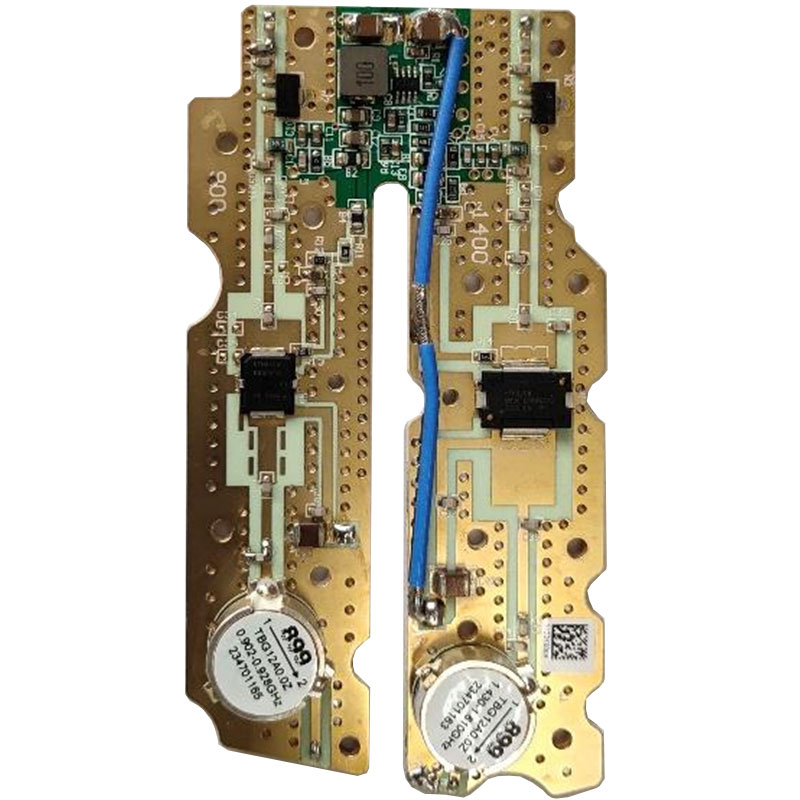

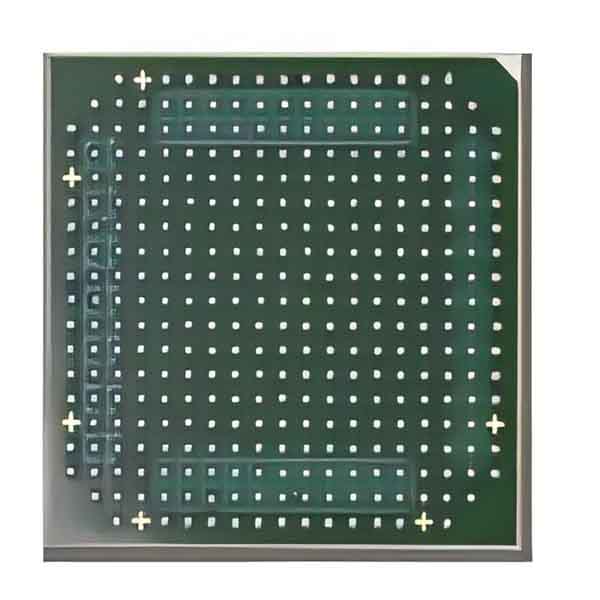

Модуль цифровой обработки

Модуль цифровой обработки -

XZPM4644M

XZPM4644M -

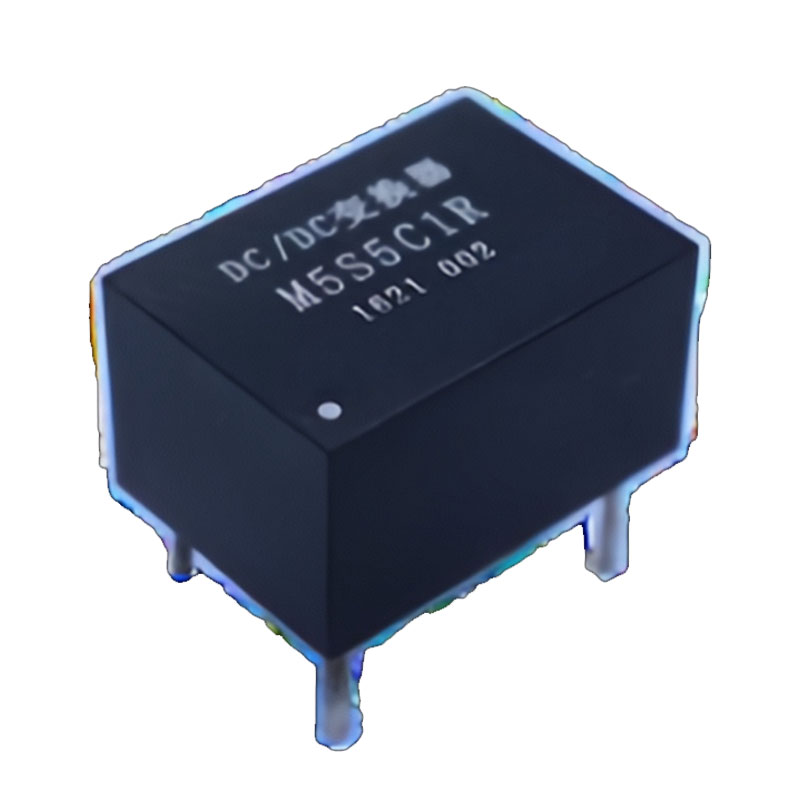

M5S5C1R

M5S5C1R -

Усилитель мощности ZPA960M1250-1000/1500

Усилитель мощности ZPA960M1250-1000/1500 -

WDM67106EC

WDM67106EC -

XAD9694QN

XAD9694QN

Связанный поиск

Связанный поиск- Центральный процессор компьютера поставщики

- Микросхема стабилизатор поставщик

- Датчик микроконтроллере поставщик

- Китай электронные компоненты какие производители

- Китай потребляемая мощность производитель

- интегральная схема питания

- Электронные преобразователи сигналов производители

- Китай цифровая плата поставщик

- Ведущий микроконтроллеры avr производитель

- Электронный блок преобразователя производители