Ведущий проектирование интегральных схем

Когда слышишь ?ведущий проектирование интегральных схем?, многие сразу представляют себе человека, который просто раздает задания и составляет графики. Это, конечно, часть работы, но суть — совсем в другом. На самом деле, это постоянное балансирование между архитектурным замыслом, физическими ограничениями кремния и… сроками, которые всегда горят. Мой опыт подсказывает, что ключевая задача — не просто ?вести?, а быть тем самым связующим звеном, которое понимает, почему аналоговый блок не встанет на цифровое ядро, и как это исправить, пока проект не ушел в тиражирование с фатальной ошибкой.

Архитектура и первый камень преткновения

Всё начинается со спецификаций. Помню один проект для телекоммуникационного модуля, где заказчик требовал немыслимую энергоэффективность на высоких частотах. Архитекторы нарисовали красивую блок-схему, но при первом же приближенном анализе помех стало ясно: выбранная топология памяти съест все преимущества. Пришлось не просто ?вести? обсуждение, а буквально разложить по полочкам моделирование, показать, где прогнозы симуляции разойдутся с реальностью. Это тот момент, когда ведущий проектирование интегральных схем должен иметь достаточно глубокий бэкграунд, чтобы оспорить даже авторитетное мнение, иначе команда потратит месяцы впустую.

Частая ошибка — недооценка этапа верификации. Многие думают, что это рутина для junior-ов. А по факту, именно здесь кроются самые коварные баги. У нас был случай с блоком управления питанием, который в симуляции работал идеально, а на кремнии уходил в latch-up при определенной температуре. Проблема была в неучтенном паразитном p-n-p переходе, который не ловился стандартными проверками DRC. После этого я всегда настаиваю на выделении отдельного ресурса под corner-анализ именно для аналоговых островков в цифровом море.

И вот здесь стоит упомянуть про сторонние решения. Иногда проще и надежнее использовать готовые, верифицированные блоки или услуги специализированных партнеров. Например, для одного из последних проектов по промышленной автоматизации мы взаимодействовали с компанией ООО Шицзячжуан Чжунчжичуансинь Технологии (https://www.zzcxkj.ru). Их профиль, включающий технический обмен, передачу технологий и, что важно, проектирование интегральных схем, оказался полезен при доработке интерфейсной части. Не всегда есть смысл изобретать всё с нуля внутри команды, особенно когда нужна узкая экспертиза по силовой электронике или специфичным интерфейсам.

?Грязные? детали: от netlist до GDSII

Переход от RTL к gate-level — это магия, которая часто пахнет потом. Тайминги, clock domain crossing, testability… Казалось бы, всё автоматизировано. Но инструменты тоже ошибаются, или их настройки оказываются неоптимальными. Однажды скрипт для вставки scan-цепей ?съел? критический путь, и мы получили violation в 0.3 нс уже на этапе P&R. Пришлось вручную править constraints и буквально сидеть с инженером по синтезу, перебирая варианты. Это та самая ?ведущая? роль — не дать проблеме уплыть на следующий этап.

Физическое проектирование — отдельная вселенная. Здесь ведущий проектирование уже должен думать как технолог. Floorplanning, размещение блоков, разводка шин питания — каждое решение имеет последствия. Помню, как сэкономили площадь, поставив чувствительный аналоговый блок рядом с цифровым шумным ядром. Результат — деградация SNR. Пришлось перекраивать план, жертвуя временем, но спасая функциональность. Это урок: компромиссы между площадью, производительностью и помехоустойчивостью нельзя принимать только на бумаге.

Взаимодействие с фабрикой — это всегда дипломатия. Представление GDSII — не финиш. Приходят вопросы по DRC, по моделям для LVS. Иногда технологические нормы меняются прямо в процессе. Нужно быстро оценить, повлияет ли это на наши спецификации, и дать четкий ответ производственникам. Задержка в день может стоить недели переноса всего графика. Здесь пригождается опыт и понимание полного цикла, от идеи до кристалла.

Случай из практики: когда теория встретилась с реальностью

Хочу привести пример, который хорошо иллюстрирует всю цепочку ответственности. Разрабатывали контроллер для системы точного позиционирования. Заказчик — производитель промышленного оборудования. Архитектура была сложной, с элементами машинного обучения на кристалле для предсказания отказов.

На этапе предварительного моделирования всё было прекрасно. Но когда получили первые прототипы с фабрики, столкнулись с аномальным саморазогревом в одном из режимов. Дебаг занял недели. Оказалось, что в симуляции мы не учли активность определенных цепей в standby-режиме, которая в реальном кремнии из-за технологических разбросов приводила к возникновению паразитных токовых петель. Это не было ошибкой инструментов или команды в классическом смысле — это был пробел в методике верификации для такой гибридной архитектуры.

Решение было неэлегантным, но рабочим: пришлось вносить изменения в firmware, чтобы избегать этого проблемного режима, и закладывать маску на изменение металлизации для следующей ревизии кристалла. Это стоило денег и репутации. Вывод? Ведущий проектирование интегральных схем должен фанатично относиться к созданию и проверке сценариев работы ?на краю? спецификаций. Недостаточно тестировать только nominal case.

Инструменты и сотрудничество: без чего нельзя

Говоря об инструментах, часто фокусируются на CAD-системах от больших вендоров. Это важно, но не менее важны внутренние скрипты, методики, checklists. Мы, например, разработали свой набор скриптов для быстрого анализа покрытия функциональной верификации, который стал неоценимым подспорьем. Иногда простая автоматизация рутины спасает от человеческого фактора.

Ни один проект не делается в вакууме. Особенно когда речь заходит о комплексных системах, где микросхема — лишь один из компонентов. Здесь важно наладить диалог с разработчиками печатных плат, системными инженерами, специалистами по ЭМС. В контексте поиска решений или партнерств для таких комплексных задач можно обратиться к компаниям с широким технологическим профилем. Та же ООО Шицзячжуан Чжунчжичуансинь Технологии, согласно информации с их сайта https://www.zzcxkj.ru, занимается не только проектированием интегральных схем, но и продажей промышленных управляющих компьютеров, интеграцией систем. Такое сочетание компетенций может быть полезно для сквозного решения, когда нужно не просто отдать чип, а убедиться, что он корректно работает в конечном устройстве.

Важный момент — управление знаниями. В больших проектах часть команды может меняться. Если ведущий не обеспечил преемственность, не документировал ключевые решения (особенно те, что были приняты как компромисс), новый сотрудник может на ровном месте наступить на те же грабли. Я завел правило проводить короткие итоговые сессии после каждого major milestone, где фиксируем не только что сделали, но и почему отклонились от первоначального плана.

Вместо заключения: что это такое на самом деле

Так что же такое ведущий проектирование интегральных схем в моем понимании сейчас, после нескольких успешных (и не очень) запусков в кремний? Это прежде всего предвидение. Предвидение технических проблем на три шага вперед. Понимание, где можно срезать угол, а где — ни в коем случае. Умение говорить на разных языках: с маркетологами — о возможностях, с архитекторами — о компромиссах, с инженерами — о деталях, с менеджментом — о рисках.

Это постоянное обучение. Техпроцессы меняются, инструменты обновляются, появляются новые архитектурные тренды вроде чиплетов или специализированных ускорителей. Останавливаться нельзя.

И наконец, это принятие ответственности. Когда с конвейера сходит пластина с твоим чипом, ты понимаешь, что за каждой точкой на этой пластине стоят тысячи принятых решений, больших и малых. И если что-то пошло не так — винить в конечном счете можно только себя, потому что именно ты вёл этот проект от первой строчки кода до финального GDS. Это тяжело, но в этом и есть вся суть и притягательность этой работы. Не административной, а глубоко инженерной и лидерской одновременно.

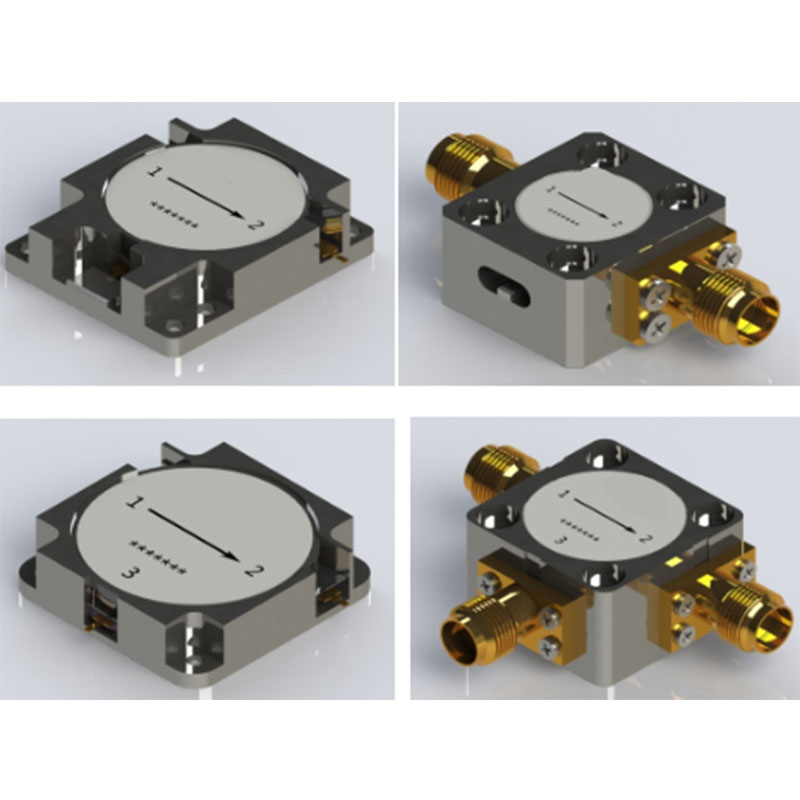

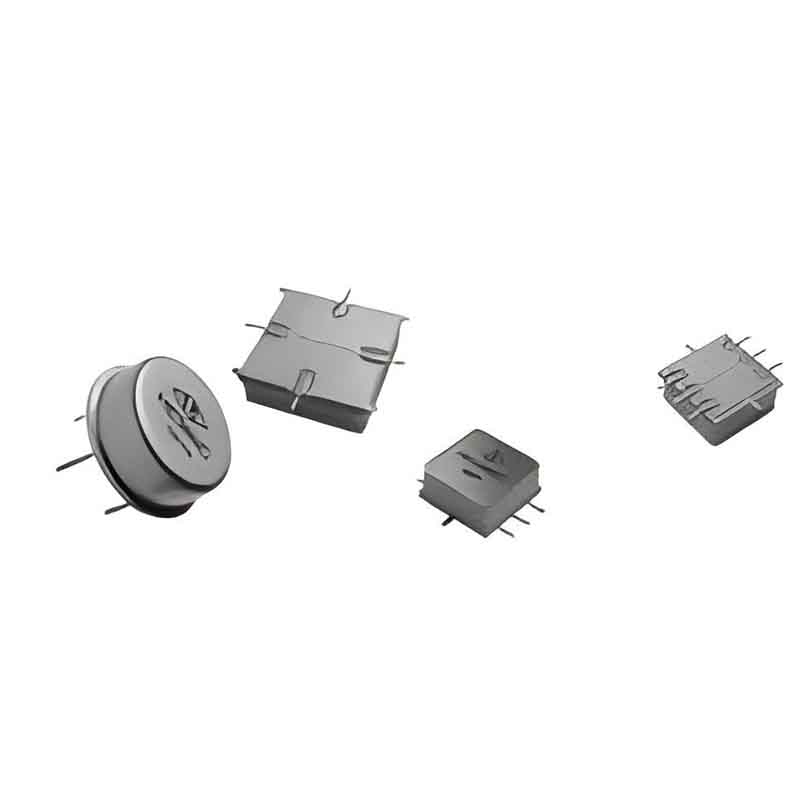

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

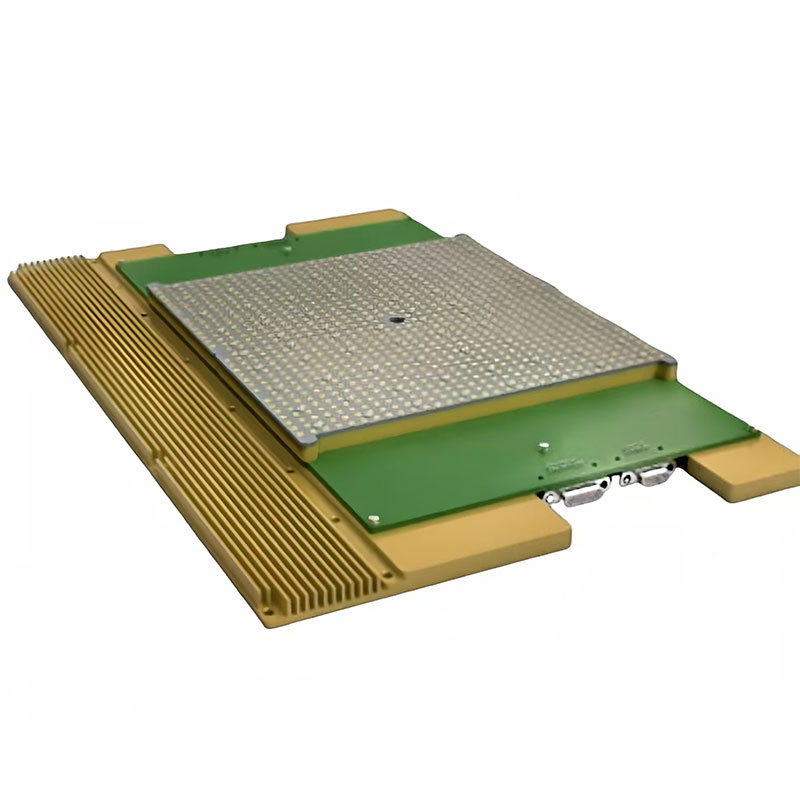

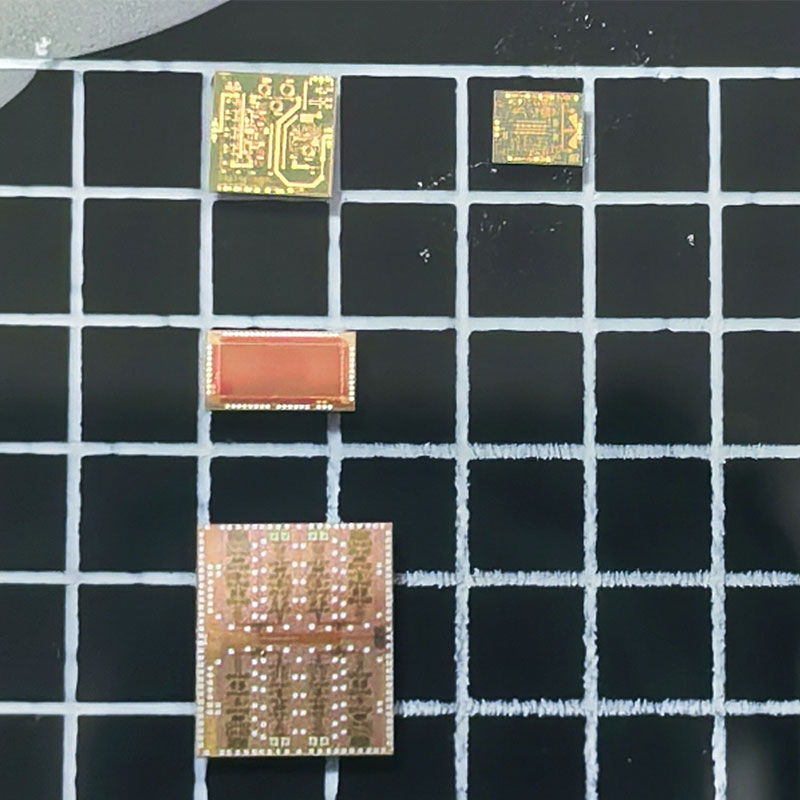

Передняя часть радиочастотного приемника c фазированной антенной решеткой K-диапазона

Передняя часть радиочастотного приемника c фазированной антенной решеткой K-диапазона -

YX110156-1216P43

YX110156-1216P43 -

CWQ2P100T

CWQ2P100T -

Представление бытовой системы накопления энергии EVE

Представление бытовой системы накопления энергии EVE -

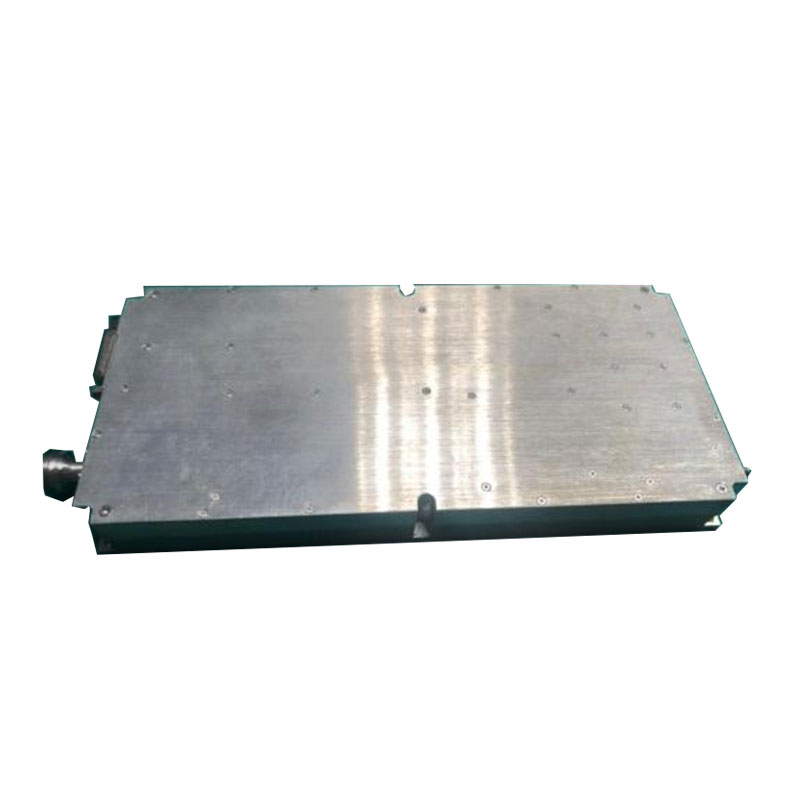

Усилитель мощности — S-диапазон ZPA2700M3500-100

Усилитель мощности — S-диапазон ZPA2700M3500-100 -

Трехкомпонентный усилитель мощности X-диапазона

Трехкомпонентный усилитель мощности X-диапазона -

VI600H28S28TNLB-G

VI600H28S28TNLB-G -

CWQ2P325T

CWQ2P325T -

Модульный источник питания

Модульный источник питания -

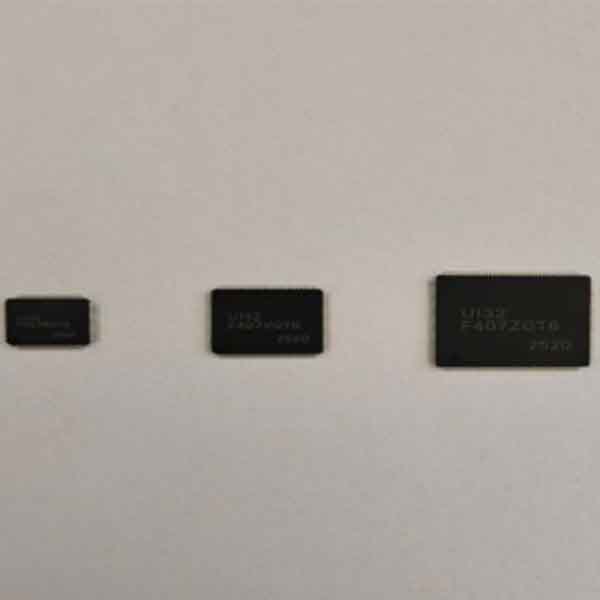

UI32F407xExG

UI32F407xExG -

XAD7606

XAD7606 -

A коробка

A коробка

Связанный поиск

Связанный поиск- Китай наземная станция производители

- Китай электронный регулятор напряжения производитель

- Ведущий наземная станция производители

- Электронный преобразователь частоты поставщик

- Ведущий цифровой сигнальный процессор производители

- Радиопоглощающий материал

- Ведущий операционный усилитель схема производитель

- Китай электронный смеситель поставщики

- Ммвч микросхема производители

- Китай рч переключатель поставщики