Ведущий сигнальный процессор

Когда говорят ?ведущий сигнальный процессор?, многие сразу представляют себе какую-то магическую черную коробочку, которая всё делает сама. Особенно в среде менеджеров, далёких от железа. Сразу начинаются разговоры о ?ключевом элементе системы?, ?высокой производительности? и прочей лапше. А на деле, в 80% случаев, проблема не в том, чтобы выбрать самый мощный DSP, а в том, чтобы заставить его стабильно работать в конкретном контуре, с конкретными датчиками, которые шумят так, что хоть святых выноси. И вот тут вся эта ведущая роль оборачивается другой стороной – он становится ?ведущим? по количеству часов, потраченных на отладку. Лично для меня ведущий сигнальный процессор – это прежде всего узел ответственности. Если сгорит простой контроллер – ну, поменяем. Если заглючит этот – вся система встанет. Поэтому выбор и работа с ним – это всегда история с приправами из стресса и кофе.

Не мощность, а совместимость: первый урок

Помню один из ранних проектов по модернизации старого испытательного стенда. Задача – заменить аналоговую систему управления виброприводом на цифровую. Заказчик требовал ?самое современное и быстрое?. Выбрали, по совету одного дистрибьютора, довольно навороченный процессор от TI. Цифры в даташите впечатляли. А потом началось…

Выяснилось, что родные АЦП этого чуда техники имели нелинейность в том самом диапазоне частот, который был критичен для нашей задачи. Шумы наводок с силовых цепей, которые старая аналоговая схема просто игнорировала, цифровой тракт воспринимал ?на ура?. Пришлось городить дополнительные каскады аналоговой фильтрации, переразводить плату. Время ушло, бюджет распух. А всё потому, что погнались за красивыми гигафлопсами, забыв спросить у железа, как оно будет общаться с реальным миром. Ведущий сигнальный процессор должен не доминировать в спецификации, а служить мостом. И характеристики этого моста – полоса пропускания, уровень шума, стабильность опорного напряжения – часто важнее чистой математической мощи.

Сейчас, когда ко мне обращаются из компаний вроде ООО Шицзячжуан Чжунчжичуансинь Технологии (их сайт https://www.zzcxkj.ru я иногда просматриваю в поисках интересных аппаратных решений), с вопросами по интеграции систем, я первым делом спрашиваю про periphery: какие датчики, какие исполнительные механизмы, какая среда. Потому что их сфера – техническое развитие, передача технологий, продажа промышленных управляющих компьютеров – как раз и предполагает, что конечное решение будет работать в ?полевых? условиях, а не в идеальной лаборатории. И там цена ошибки в выборе процессора высока.

Программная обвязка: где кроется дьявол

Хорошо, с железом определились. Дальше – ПО. И вот здесь, в моём опыте, провалов было даже больше. Производители любят хвастаться богатыми библиотеками и удобными средами разработки. На бумаге. На практике же оказывается, что драйвер для нужного интерфейса SPI или Ethernet написан с допущениями, которые в твоей схеме не работают. Или компилятор оптимизирует критичный по времени кусок кода так, что в нём появляется латентность, ломающая весь цикл управления.

Был случай с разработкой блока управления для прецизионного электропривода. Использовали процессор с ядром ARM и DSP-расширениями. Всё отлично работало в симуляции и на стенде при пошаговом выполнении. В реальном времени, под нагрузкой, система периодически ?задумывалась?. Два дня ловили. Оказалось, что обработчик прерывания от энкодера, написанный на С, при определённых условиях вызывал неявное сохранение/восстановление слишком большого контекста процессора, что съедало драгоценные микросекунды. Пришлось переписывать этот кусок на ассемблере, вручную контролируя каждую операцию. После этого я всегда закладываю время на ?притирку? ПО к конкретному ведущему сигнальному процессору. Никакие абстрактные бенчмарки не заменят тестов в целевой конфигурации.

Это, кстати, область, где консультационные услуги, подобные тем, что указаны в описании ООО Шицзячжуан Чжунчжичуансинь Технологии, могли бы быть очень кстати. Не просто продать железо, а помочь с прохождением этого тернистого пути от чистого листа в IDE до стабильного промышленного кода. Технический обмен и консультирование на таком уровне – это огромная ценность.

Тепло и надёжность: скучная необходимость

Об этом пишут везде, но почему-то постоянно наступают на одни и те же грабли. Тепловыделение. Особенно когда пытаешься выжать из процессора все соки для алгоритмов цифровой фильтрации в реальном времени. Красиво рассчитал, что средняя нагрузка 70%, радиатор по даташиту подобрал. А в реальности алгоритм работает рвано, короткими пиками в 100% нагрузки. И эти пики греют кристалл локально и быстро. Через полгода работы на объекте начинаются странные глюки, которые пропадают после остывания.

Пришлось учиться смотреть не на средние температуры, а на тепловые карты корпуса и динамику. Иногда решение было парадоксальным: искусственно замедлить часть вычислений, ввести более плавную нагрузку, но зато добавить пассивный теплоотвод попроще. Надёжность системы в итоге выигрывала у теоретической пиковой производительности. Ведущий сигнальный процессор должен вести систему годами, а не только в момент презентации. И этот аспект напрямую пересекается с продажей электронных компонентов и оборудования для электромеханической сборки – цепочка поставки должна включать не просто чип, а проверенное решение по его теплоотводу и энергоснабжению в сборе.

Интеграция в систему: финальный барьер

Допустим, твой модуль с процессором идеален. Но его же надо встроить в большую систему. И вот тут начинается танце с протоколами обмена, гальванической развязкой, согласованием уровней. Часто заказчик хочет, чтобы ?ведущий? модуль собирал данные с десятка подчинённых устройств по разным интерфейсам: CAN, RS-485, Ethernet. И для каждого нужен свой драйвер, свой стек протоколов.

Одна из самых неприятных находок – когда конфликтуют сами драйверы внутри ОСРВ или даже в bare-metal системе. Прерывание от сетевого контроллера может надолго блокировать доступ к памяти, которую в этот момент ждёт контроллер CAN для отправки критичной команды. Проектирование интегральных схем и разработка ПО, которые заявлены в деятельности многих технологических компаний, должны учитывать эту системную, целостную картину. Нельзя просто взять и склеить лучшие куски кода из интернета – они начнут воевать за ресурсы того самого ведущего сигнального процессора.

Порой проще и надёжнее оказывается развязать задачи физически: поставить второй, более простой контроллер для обработки медленных или критичных по времени протоколов, а основному DSP оставить только тяжёлую математику и стратегическое управление. Это кажется избыточным, но повышает надёжность на порядок.

Взгляд в будущее: не зацикливаться на настоящем

Технологии меняются. То, что сегодня является топовым ведущим сигнальным процессором, через три года устареет морально, а через пять – может исчезнуть с производства. Это боль для любого инженера. Поэтому сейчас, при выборе платформы, я всё чаще смотрю не на пиковую производительность, а на экосистему: насколько живое сообщество, продолжает ли производитель выпускать обновления компиляторов и библиотек, есть ли миграционные пути к newer поколениям.

И ещё один момент – тенденция к гетерогенным вычислениям. Всё чаще тот самый ?ведущий? процессор – это не один кристалл, а связка из CPU, DSP-блоков и FPGA на одной подложке. Управление таким зверем – это уже следующая ступень сложности. Но за этим, вероятно, будущее в областях, связанных с проектированием интегральных схем и продвижением технологий, как у упомянутой компании. Возможность программно переопределять часть аппаратной логики под конкретную задачу – это мощнейший инструмент.

В итоге, работа с ведущим сигнальным процессором – это постоянный баланс. Баланс между мощностью и надёжностью, между красотой алгоритма и суровостью его реализации, между требованиями сегодняшнего дня и возможностями завтрашнего. Это не про то, чтобы найти ?самый лучший?. Это про то, чтобы найти ?самый подходящий? для данной системы, в данных условиях, и заставить его работать так, чтобы о нём забыли. Потому что если о нём не вспоминают – значит, он действительно хорошо ведёт.

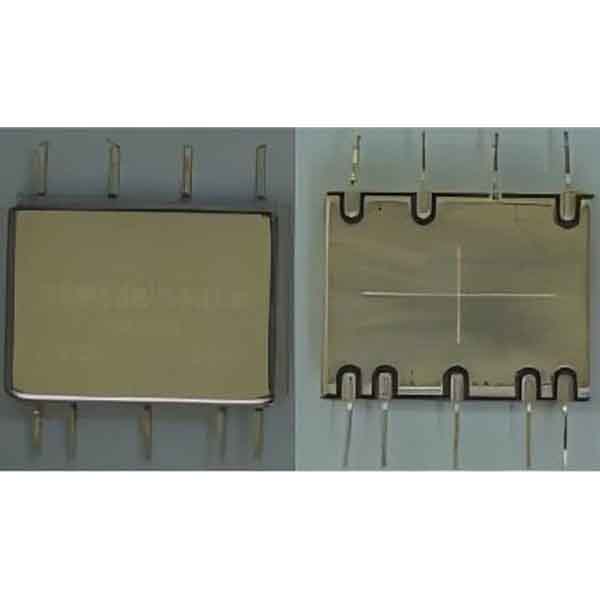

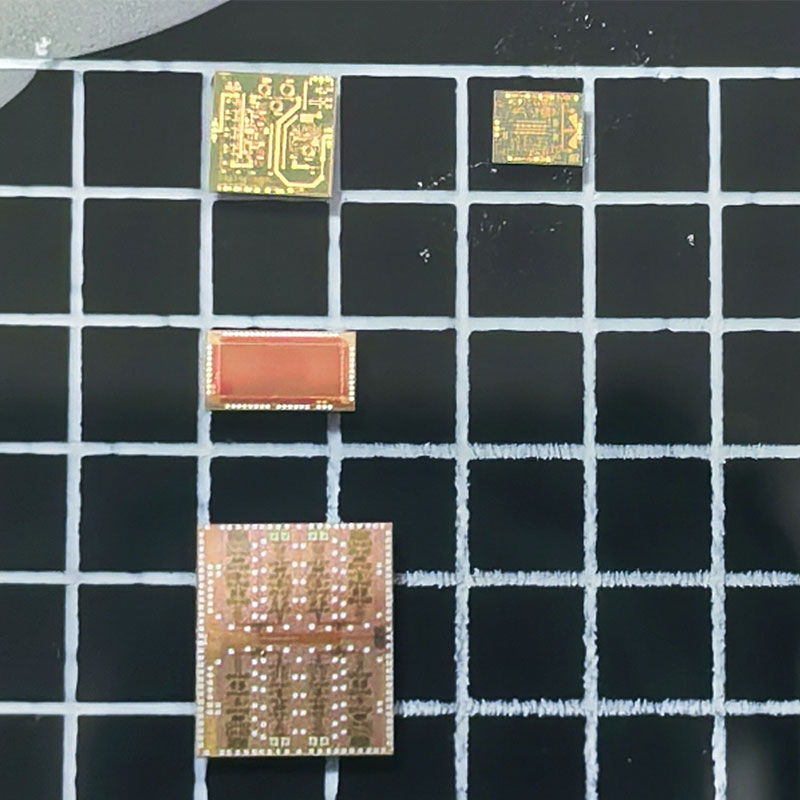

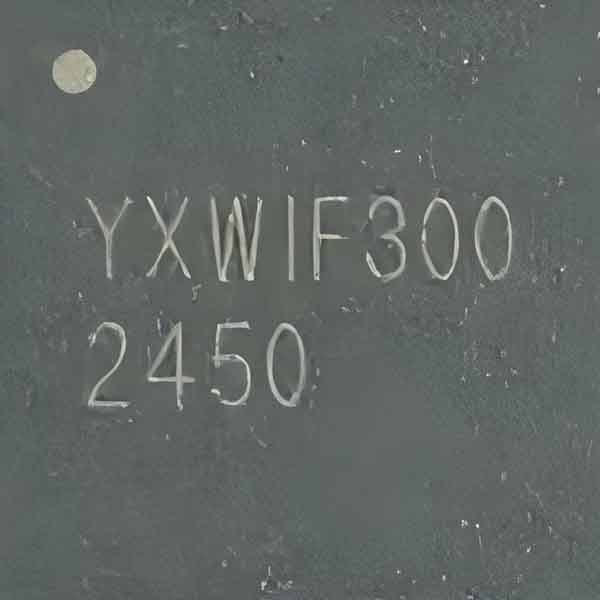

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продуктыСвязанный поиск

Связанный поиск- Ведущий микросхемы контроллеры производители

- Высококачественный логическая интегральная схема

- Ведущий память центрального процессора

- Китай материал с фазовым переходом поставщики

- Китай модуль преобразования частоты производители

- Центральный процессор персонального производители

- Китай ограничительный усилитель производители

- Электронные запоминающие устройства производители

- Китай цифровая плата

- Датчик микроконтроллере производитель