Ведущий схемы микросхем

Когда говорят ?ведущий схемы микросхем?, многие сразу представляют себе того, кто рисует дорожки в CAD-системе. Это, конечно, часть работы, но суть — глубже. Это скорее человек, который определяет, как сигнал пойдёт от точки А к точке Б, учитывая десятки ?но?: помехи, задержки, тепловыделение, стоимость производства. Я сам долго думал, что это чисто инженерная задача, пока не столкнулся с ситуацией, когда идеальная по учебникам разводка приводила к сбоям в серии. Потому что в жизни чип работает не в вакууме, а на плате, рядом с другими компонентами, в корпусе, который может греться. Вот об этих нюансах, которые не пишут в мануалах, и хочется порассуждать.

От абстракции к кремнию: где кроется главная сложность

Начинается всё, казалось бы, просто: есть принципиальная схема, есть библиотека компонентов. Берёшь и соединяешь. Но первый же камень преткновения — выбор технологии и фабрики-изготовителя. У каждой — свои design rules, свои ограничения на минимальную ширину линии, зазоры, плотность контактов. Однажды для проекта по силовой электронике мы рассматривали вариант с российской фабрикой, но их нормы для высоких напряжений оказались слишком консервативными, пришлось бы увеличивать кристалл раза в полтора, что убивало экономику проекта. Пришлось искать альтернативу в Азии, но это породило кучу вопросов по логистике и контролю качества.

И вот здесь часто возникает разрыв между проектированием и реальностью. Ты можешь сделать красивую, компактную схему, но если она не учитывает технологические допуски конкретного производства, выход годных на тестовых пластинах упадёт катастрофически. Я помню, как мы оптимизировали layout под максимальную скорость, использовали самые тонкие линии, но не учли, что при массовом травлении возможен небольшой underetch. В результате на партии линии в критичных местах стали тоньше расчётного, сопротивление выросло, и тайминги ?поплыли?. Урок был дорогой, но показательный: ведущий схемы должен постоянно держать в голове не идеальную картинку с монитора, а грязный, неидеальный процесс изготовления.

Особенно критично это для аналоговых блоков или блоков питания. Там, где идут высокие токи или чувствительные слаботочные сигналы, разводка — это 80% успеха. Нельзя просто ?развести соединения?. Надо думать о путях возврата тока, о помехах от цифровых линий, о падении напряжения на шинах питания. Часто приходится идти на компромиссы: например, удлинять путь, чтобы обойти шумную зону, или добавлять лишние декoupling-конденсаторы, жертвуя площадью. Это постоянный trade-off.

Инструменты и их ограничения: почему CAD — не панацея

Все работают в Cadence Virtuoso, Synopsys IC Compiler или чём-то подобном. Инструменты мощные, с автораутингом, симуляцией на уровне parasitic extraction. Но слепо доверять им нельзя. Автоматический роутер, особенно для сложных смешанных сигнальных схем, часто выдаёт формально правильный, но с инженерной точки зрения ущербный результат. Он может проложить чувствительную аналоговую линию параллельно тактовому сигналу на три миллиметра — по правилам нарушения нет, но на практике наводки гарантированы.

Поэтому основная работа часто идёт в ручном или полуручном режиме. Сначала ведущий схемы определяет критичные пути, шины питания, аналоговые островки — и разводит их вручную, задавая жёсткие ограничения. Потом уже отдаёт на автораутинг менее критичные цифровые блоки. И даже после этого нужна тщательная верификация — не только DRC (Design Rule Check) и LVS (Layout vs Schematic), но и анализ паразитных параметров, электромиграции, IR-дропа. Симуляция пост-лайаута — это святое. Бывало, что схема идеально работала в pre-layout симуляции, а после извлечения паразитов из готового layout частота среза операционного усилителя падала на 30%. И всё из-за паразитной ёмкости длинной линии к выходному каскаду.

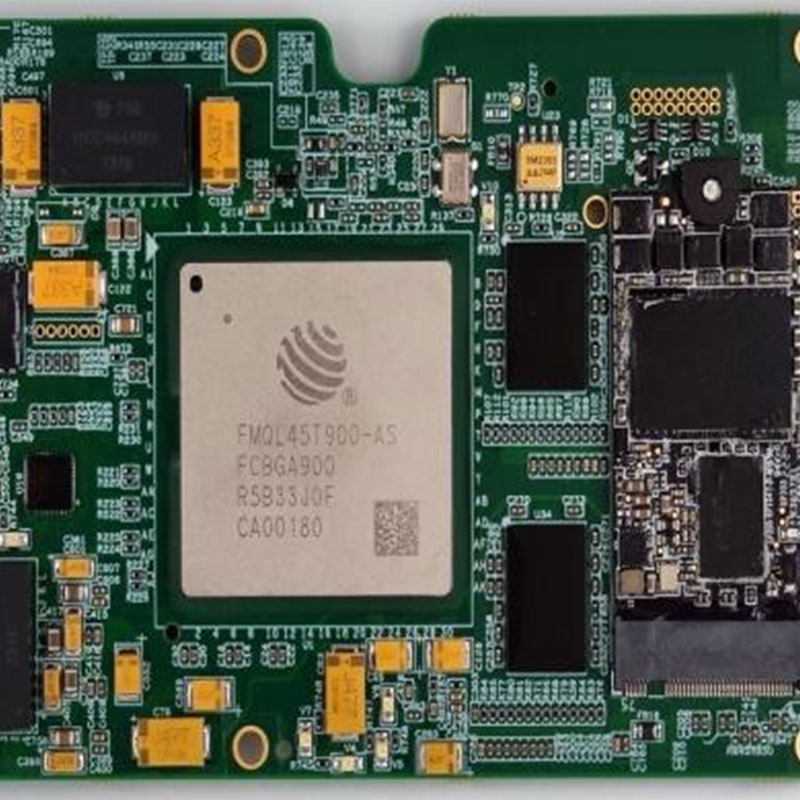

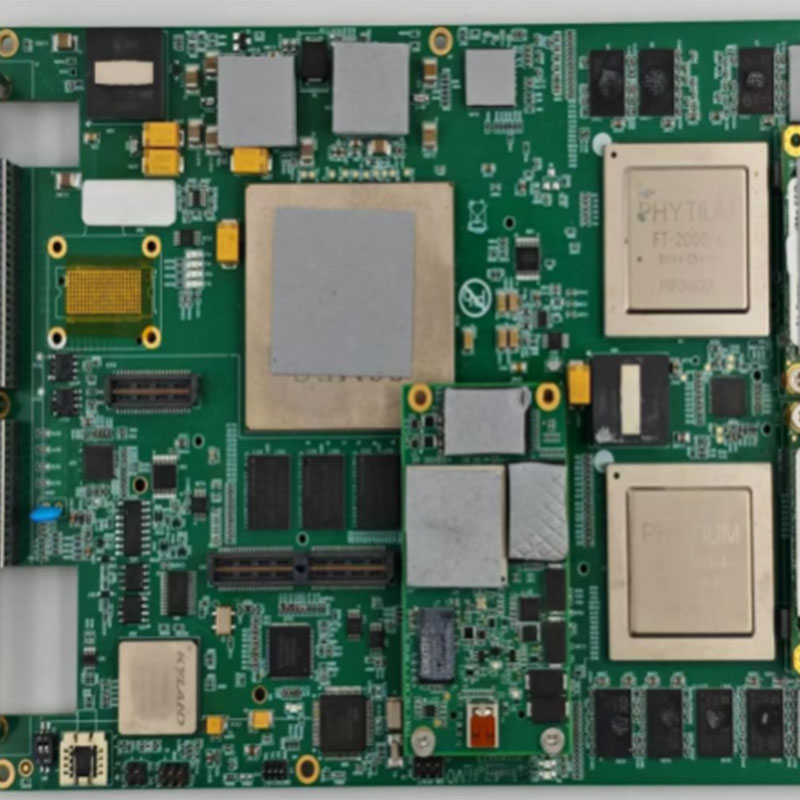

Ещё один момент — работа с библиотеками стандартных ячеек и IP-блоками. Часто компании, вроде той же ООО Шицзячжуан Чжунчжичуансинь Технологии, которая занимается техническим консультированием и передачей технологий, могут выступать как интеграторы или разработчики специализированных решений. Они не всегда делают чип с нуля, а могут брать готовые лицензионные IP-блоки (например, процессорное ядро, интерфейс USB) и ?обвязывать? их своей логикой. Задача ведущего схемы в таком случае — грамотно вписать эти блоки в общую топологию, обеспечить для них корректные условия по питанию, заземлению и синхронизации. Иногда IP-блок поставляется как ?чёрный ящик? с готовым, неоптимальным layout, и его приходится обходить, как скалу.

Случай из практики: когда сэкономили на симуляции

Хочется привести конкретный пример, не из учебника. У нас был проект контроллера для промышленного управляющего компьютера — что-то на стыке деятельности, которую как раз декларирует ООО Шицзячжуан Чжунчжичуансинь Технологии: продажа промышленных управляющих компьютеров и систем, проектирование интегральных схем. Нужен был интерфейсный чип с несколькими каналами АЦП и ЦАП, работающий в широком температурном диапазоне. Сроки горели, и на этапе разводки аналоговой части решено было сэкономить время на полной post-layout симуляции всех режимов. Проверили только типовой случай при комнатной температуре.

Чипы пришли, начались испытания. При +85°C в одном из каналов АЦП начались необъяснимые нелинейные искажения. Долгие поиски привели к узкому месту: путь опорного напряжения к компаратору внутри АЦП был разведён слишком длинной и тонкой линией, которая проходила рядом с выходным буфером цифровой шины. При нагреве сопротивление линии росло, падение напряжения на ней увеличивалось, а из-за соседства с цифровым трактом добавлялись помехи по питанию. В pre-layout модели этого не было, паразиты были, но их влияние при высокой температуре не оценили. Пришлось экранировать линию на уже готовом layout, добавляя слои металла поверх, что увеличивало стоимость. Но перевыпускать маску — было бы ещё дороже. Этот провал научил меня, что экономия на симуляции, особенно для изделий с жёсткими внешними условиями, — это прямая дорога к дополнительным затратам и репутационным рискам.

Взаимодействие со смежниками: без этого никуда

Работа ведущего схемы микросхем — не изоляция. Это постоянный диалог. С разработчиком архитектуры — чтобы понять приоритеты сигналов. С схемотехником — чтобы уточнить чувствительные узлы и допустимые паразитные параметры. С технологическим отделом или внешним фаундри — чтобы согласовать все нормы и получить адекватные модели для симуляции. И, что очень важно, с тестировщиками (test engineers).

Ещё на этапе проектирования layout нужно закладывать тестовые структуры (test structures) и точки контроля (probing pads). Как потом будет проводиться тестирование пластины на фабрике? Как будут отбраковываться бракованные кристаллы? Если не предусмотреть удобные точки для контактных щупов или не вывести критичные внутренние сигналы на тестовые выводы, то диагностика проблем на этапе производства превратится в кошмар. Однажды мы столкнулись с низким выходом годных по непонятной причине — все чипы ?зависали? при определённой команде. Только благодаря тому, что у нас были выведены внутренние сигналы с блока управления памятью, удалось быстро локализовать проблему до конкретного инвертора, страдавшего от electromigration из-за плохо рассчитанной ширины дорожки в этом месте.

Сегодня многие компании, особенно занимающиеся техническим консультированием и комплексными решениями, как упомянутая на https://www.zzcxkj.ru, часто работают как связующее звено между заказчиком с идеей и фабрикой-изготовителем. В такой роли ведущий схемы становится ключевой фигурой, которая должен не только технически грамотно выполнить разводку, но и понимать бизнес-ограничения, сроки, возможности производства. Его решения напрямую влияют на себестоимость и надёжность конечного продукта, будь то силовой электронный компонент или коммуникационное оборудование из сферы их деятельности.

Взгляд в будущее: что меняется в профессии

Техпроцессы продолжают уменьшаться. Переход на нормы 28 нм, 16 нм, а теперь уже и меньше — это не просто более мелкие транзисторы. Это принципиально иная физика. Влияние паразитных эффектов, таких как capacitive coupling и inductive crosstalk, становится доминирующим. Ручная разводка на таких технологиях без глубокого симуляционного сопровождения на каждом шагу практически невозможна. Инструменты для анализа SI/PI (Signal Integrity/Power Integrity) становятся must-have.

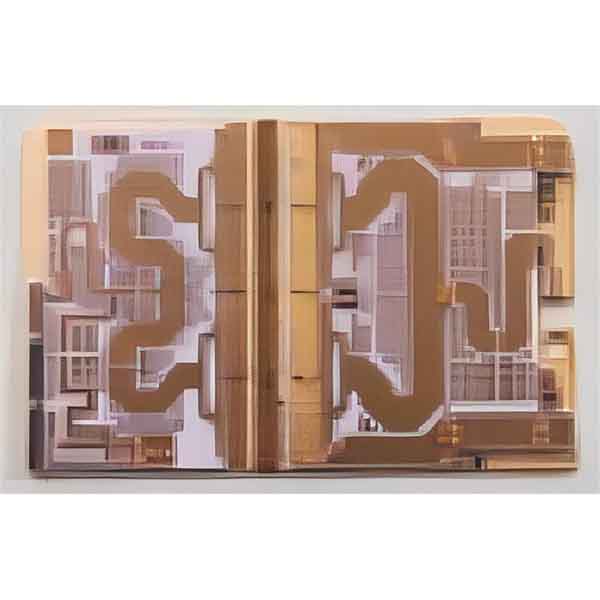

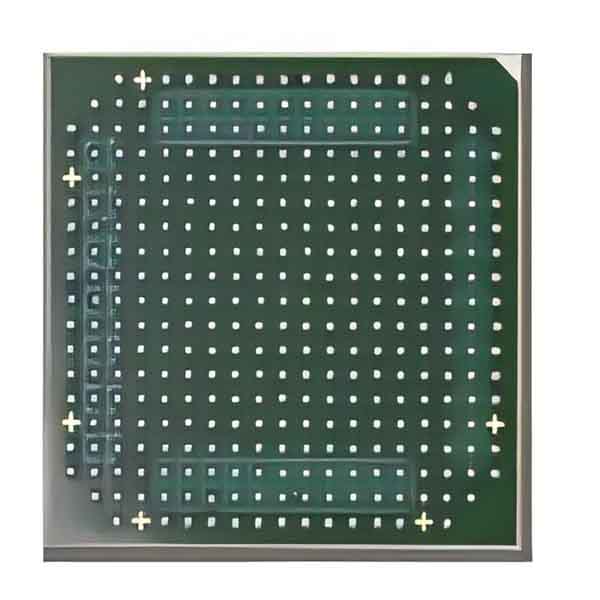

Кроме того, растёт популярность схем 2.5D и 3D-интеграции — когда несколько кристаллов (чиплетов) размещаются на общей подложке (interposer) или монтируются друг на друга. Здесь задача ведущего схемы трансформируется. Нужно думать уже не только о разводке внутри одного кристалла, но и о межкристальных соединениях через кремниевые TSV (Through-Silicon Vias) или микробампы. Проблемы синхронизации, целостности сигнала и отвода тепла многократно усложняются. Опыт в этой области пока что штучный товар.

И последнее. Всё больше задач, особенно в цифровых блоках, берут на себя алгоритмы машинного обучения, внедряемые в САПР. Они могут предлагать варианты размещения и разводки, обучаясь на успешных прошлых проектах. Но я убеждён, что финальное решение, особенно в смешанных и аналоговых схемах, всегда должно оставаться за человеком. За тем самым ведущим схемы, который может взвесить не только то, что говорит инструмент, но и тот самый ?грязный? производственный опыт, учтя который, можно избежать фатальной ошибки. Его роль не исчезает, а эволюционирует от чертёжника к стратегу, принимающему ключевые решения о физической реализации идеи в кремнии. И в этом, пожалуй, и заключается главный интерес и вызов этой работы.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продуктыСвязанный поиск

Связанный поиск- Высококачественный электронный блок преобразователя

- Китай радиодетали и электронные компоненты производитель

- Китай интегральные операционные усилители поставщики

- Китай электронный преобразователь частоты поставщик

- Ведущий логическая интегральная схема производители

- Гибридная интеграция

- Китай микрополосковый изолятор поставщик

- Цифро-аналоговый преобразователь производитель

- Источник опорной частоты поставщики

- Китай большие интегральные схемы производитель