Высококачественный проектирование интегральных схем

Когда говорят о высококачественном проектировании интегральных схем, многие сразу представляют себе передовые техпроцессы 5 нм или 3 нм. Но это, пожалуй, самый распространённый миф. Качество часто начинается не с выбора узла, а с чёткого понимания, для чего вообще эта схема нужна. Я видел проекты на 28 нм, которые по надёжности и оптимизации под задачу давали фору более ?модным? решениям. Ключ — в системном подходе, где каждый этап, от архитектурных решений до верификации и подготовки к производству, выдержан в одной логике качества. И эта логика не всегда прописана в стандартах — она часто рождается из опыта, иногда горького.

Архитектура и спецификации: где всё начинается и где чаще всего ошибаются

Первый залог качества — это не код на Verilog, а грамотно составленные спецификации. И здесь кроется ловушка: часто заказчик и инженер-проектировщик говорят на разных языках. ?Нужна высокая производительность? — это не спецификация. Нужны конкретные цифры: частота, потребление, условия работы. Я помню один проект для промышленной автоматизации, где изначально недооценили требования по температурному диапазону и помехоустойчивости. В итоге пришлось на ходу перекраивать блок аналогового интерфейса, что вылилось в задержки и перерасход средств. Теперь мы в начале любого проекта проводим глубокий анализ требований, часто вместе с партнёрами, которые лучше знают конечное применение. Например, сотрудничая с ООО Шицзячжуан Чжунчжичуансинь Технологии, мы уделяем особое внимание их сфере — интеграции систем и продаже промышленных управляющих компьютеров. Их опыт подсказывает, какие интерфейсы (те же промышленные шины) и уровни защиты от ESD критически важны для конечного устройства. Это не абстрактные пожелания, а конкретные входные данные для архитектуры.

Архитектурный выбор — это всегда компромисс. Больше быстродействия — выше потребляемая мощность. Меньшая площадь кристалла — возможно, более сложная и дорогая разводка. Здесь качество проектирования проявляется в умении найти баланс, оптимальный для конкретного продукта. Для массового IoT-сенсора главным будет ультранизкое потребление в режиме сна, а для процессора обработки сигналов в системе видеонаблюдения — предсказуемая пропускная способность. Слепое копирование решений из предыдущих проектов — путь к провалу.

И ещё один нюанс — верифицируемость архитектуры. Нужно с самого начала думать о том, как ты будешь проверять эту сложную систему на чипе. Заложить возможности для тестового доступа, встроить BIST (Built-In Self-Test) логику для памяти. Если этого не сделать на этапе высокоуровневого проектирования, потом может оказаться, что проверить работоспособность готового чипа в полном объёме невозможно без огромных затрат на тестовое оборудование.

RTL-кодирование и симуляция: дисциплина против творческого беспорядка

Переход от архитектуры к регистрово-трансферному уровню (RTL) — это область, где качество кода напрямую влияет на качество будущего кристалла. Стиль кодирования должен быть консервативным и предсказуемым для синтезатора. Излишняя ?креативность? здесь вредна. Мы придерживаемся строгих правил написания кода: никаких комбинаторных петель, чёткое разделение тактовых доменов, аккуратная работа с асинхронными сигналами. Кажется, это азбука, но сколько проблем возникает из-за их несоблюдения!

Симуляция — наш основной инструмент проверки на этом этапе. Но и здесь есть подводные камни. Полнота функционального покрытия (code coverage, functional coverage) — это не просто отчёт для галочки. Это карта, показывающая, какие части твоего дизайна действительно проверены тестами. Бывало, что проект с 95% покрытием кода ?падал? на первых же тестовых образцах из-за неучтённого углового случая (corner case) во взаимодействии блоков. Поэтому мы дополняем автоматические тесты directed tests, которые моделируют именно те сложные и маловероятные сценарии, которые могут возникнуть в реальной работе. Например, для блока связи, который будет использоваться в оборудовании, поставляемом ООО Шицзячжуан Чжунчжичуансинь Технологии, мы специально симулируем сбои питания и скачки на линиях данных.

Отдельная история — низкоуровневое моделирование аналоговых блоков в цифровой среде. Для ЦАП, АЦП, ФАПЧ часто используются поведенческие модели. Их точность критична. Однажды мы столкнулись с тем, что поведенческая модель PLL не учитывала фазовый шум вполне определённого характера, что привело к ухудшению характеристик всего приёмного тракта на кремнии. Пришлось на лету корректировать цифровую часть, чтобы скомпенсировать этот эффект. Урок: модели должны быть как можно ближе к реальности, даже если их создание отнимает время.

Синтез, верификация времени и физическое проектирование: встреча с реальностью

Синтез — это момент, когда твой RTL-код превращается в конкретную схему из элементов библиотеки. Настройка синтеза — это искусство. Нужно правильно задать ограничения (constraints): тактовые частоты, задержки на входы/выходы, условия по процессу, напряжению, температуре (PVT). Если ограничения слишком жёсткие, синтезатор может не найти решения или раздуть площадь. Если слишком мягкие — чип может не работать на нужной частоте. Мы обычно проводим синтез в нескольких угловых условиях (typical, worst-case slow, best-case fast), чтобы убедиться в устойчивости работы.

Статический временной анализ (STA) после синтеза — это обязательный и бескомпромиссный этап. Все временные нарушения (timing violations) должны быть устранены. Иногда это приводит к обратному проектированию — переписыванию критических путей на RTL-уровне. Автоматизированные инструменты для исправления нарушений (ECO) помогают, но слепо полагаться на них нельзя. Они могут ?залатать? один путь, создав проблему в другом месте или увеличив потребление.

Физическое проектирование (place & route) — это уже территория, где абстрактная схема обретает форму на кристалле. Здесь качество определяется планировкой (floorplan), размещением блоков, разводкой clock tree. Плохо сбалансированное clock tree может ?съесть? весь временной запас. Проблемы целостности сигналов (SI) — перекрёстные наводки, падение напряжения в цепях питания (IR-drop) — всё это всплывает здесь. Для проектов, которые должны работать в связке с силовыми электронными компонентами (а это как раз одна из специализаций zzcxkj.ru), анализ электромиграции и надёжности питания становится критически важным. Мы используем итеративный подход: после первоначальной разводки снова запускаем STA и симуляции с учётом паразитных параметров (post-layout simulation), и если что-то не так — возвращаемся на шаг назад.

Подготовка к производству и пост-кремниевая отладка

Генерация данных для фотошаблонов (GDSII) — финальный файл, который уходит на фабрику. Но и здесь есть свои нюансы. Проверка правил оформления (DRC) и правил электрического оформления (LRC, ERC) должна быть безупречной. Фабрики дают строгие наборы правил, и их нарушение гарантирует брак. Кроме того, мы всегда добавляем тестовые структуры на неиспользуемую площадь кристалла: TEG (Test Element Group) для проверки параметров транзисторов, дополнительные цепи для контроля процесса производства. Это страховка, которая потом помогает в отладке.

Ожидание первых образцов — самый нервный период. И вот они приходят. Post-silicon validation — это отдельная наука. Даже при идеальной предварительной проверке, чип в реальном кремнии может вести себя иначе. Нужно уметь быстро локализовать проблему: это ошибка проектирования, артефакт производства или неточность в измерительной установке? Здесь пригодятся все тестовые цепи, заложенные ранее. Опыт показывает, что проблемы редко бывают глобальными; чаще это небольшие отклонения в каком-то одном блоке, которые, однако, влияют на общие характеристики.

Например, в одном из наших проектов для сектора технического обмена и передачи технологий мы столкнулись с чуть более высоким, чем ожидалось, током утечки в определённом режиме. Анализ показал, что виноват не дизайн, а небольшое отклонение порогового напряжения в библиотеке ячеек от номинала для данной партии кремния. Проблему решили корректировкой программного обеспечения драйвера, который управлял режимами энергосбережения. Это к вопросу о важности системного подхода и гибкости.

Качество как процесс, а не как атрибут

Так что же такое высококачественное проектирование интегральных схем в итоге? Это не какая-то волшебная методика или самый дорогой инструмент. Это, скорее, культура. Культура глубокого понимания задачи, дисциплины на всех этапах работы, постоянной проверки и перепроверки своих допущений. Это умение работать в команде, где архитектор слышит специалиста по верификации, а проектировщик физического уровня понимает требования системного инженера.

Это также про осознание контекста. Чип не живёт в вакууме. Он будет впаян в плату, которая будет частью большего устройства, как те промышленные компьютеры или системы интеграции, которые являются конечным продуктом для многих наших заказчиков, включая ООО Шицзячжуан Чжунчжичуансинь Технологии. Поэтому качество нашего проектирования измеряется не только мегагерцами и милливаттами, но и тем, насколько надёжно и предсказуемо этот чип будет работать в реальном изделии, в реальных, иногда жёстких, условиях.

И последнее: качество не терпит спешки. Каждый пропущенный этап проверки, каждое ?авось сработает? — это потенциальная проблема, которая обойдётся в десятки раз дороже на этапе производства или, что хуже, в поле у конечного пользователя. Поэтому даже в условиях жёстких deadlines важно сохранять системность и не пренебрегать рутинной, но такой необходимой работой по верификации и валидации каждого решения. Это и есть настоящая профессиональная ответственность проектировщика.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

CWQ2P325T

CWQ2P325T -

Усилитель мощности ZPA960M1250-1000/1500

Усилитель мощности ZPA960M1250-1000/1500 -

Мостовой чип Loongson 7A2000

Мостовой чип Loongson 7A2000 -

WDM67102

WDM67102 -

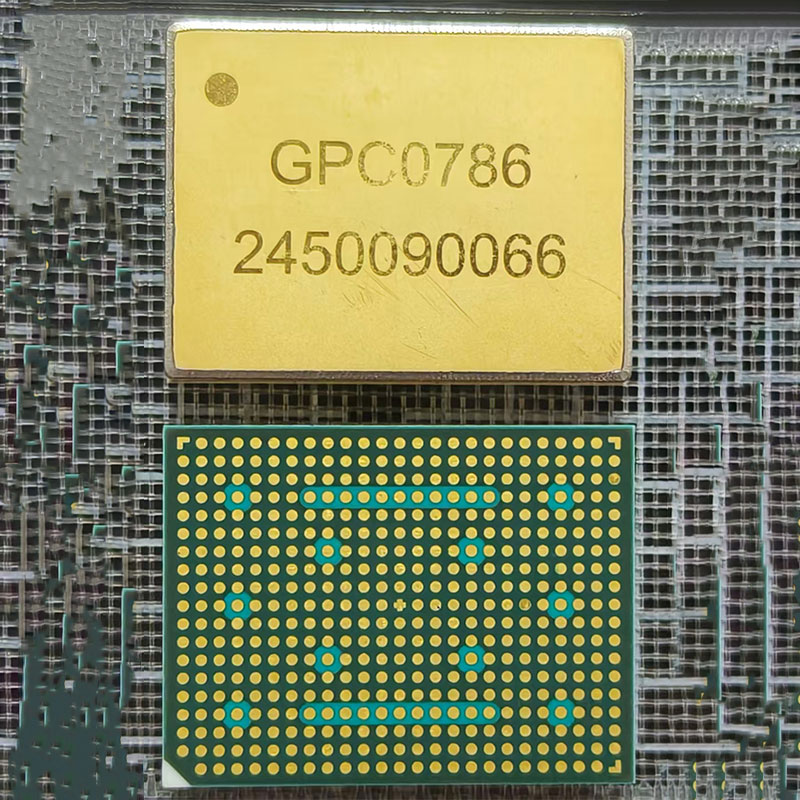

Процессор Loongson 2K2000

Процессор Loongson 2K2000 -

Система на кристалле (SoC) Loongson 2P0300

Система на кристалле (SoC) Loongson 2P0300 -

Модуль усилителя мощности (широкополосный)

Модуль усилителя мощности (широкополосный) -

Интегральный широкополосный усилитель HE380

Интегральный широкополосный усилитель HE380 -

B коробка

B коробка -

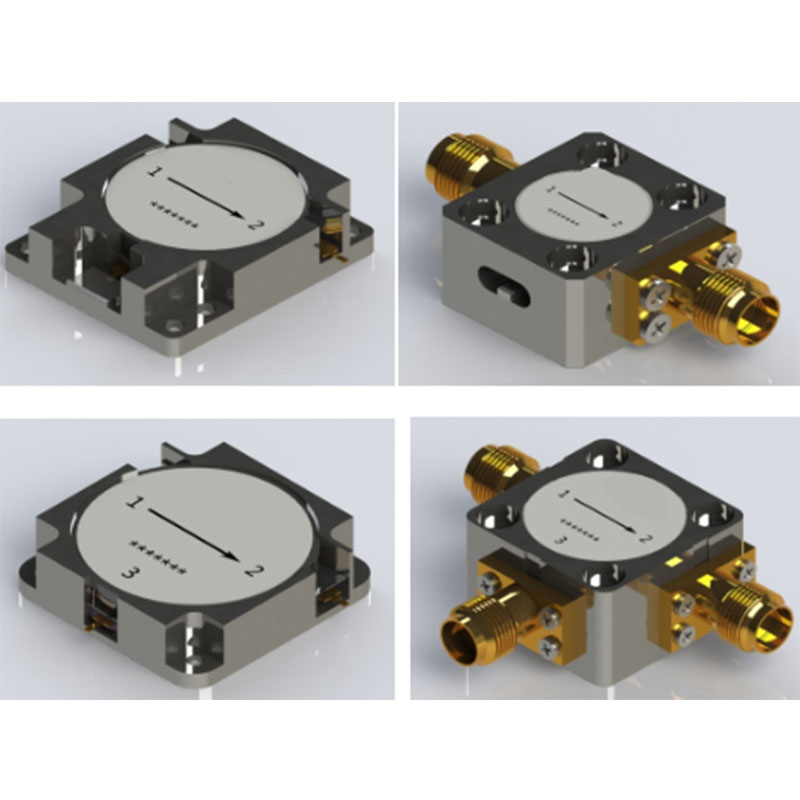

СВЧ изолятор,циркулятор

СВЧ изолятор,циркулятор -

D2000 COMe-ядро-модуль

D2000 COMe-ядро-модуль -

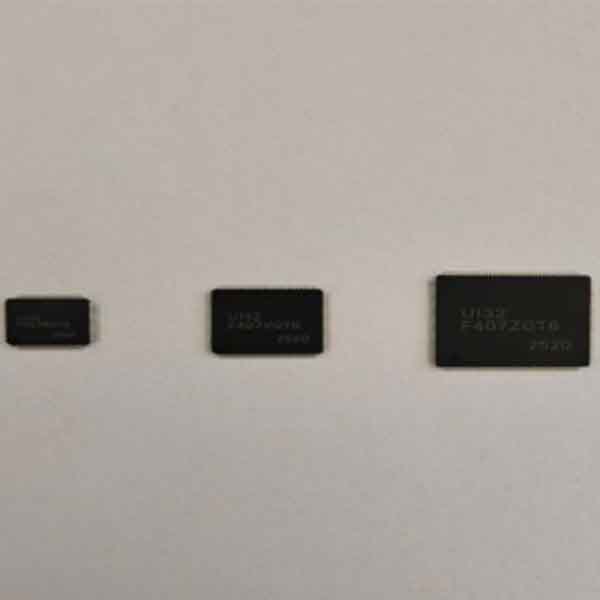

UI32F407xExG

UI32F407xExG

Связанный поиск

Связанный поиск- Электронный усилитель поставщики

- Большая интегральная схема эвм производитель

- Микросхема напряжения производитель

- Китай центральный процессор компьютера производитель

- Ведущий микросхема напряжения

- Китай источник опорной частоты поставщик

- Ведущий элементная база интегральные схемы

- Китай модуль центрального процессора

- Ведущий центральный процессор цп производитель

- Высококачественный датчик микроконтроллере