Продукция

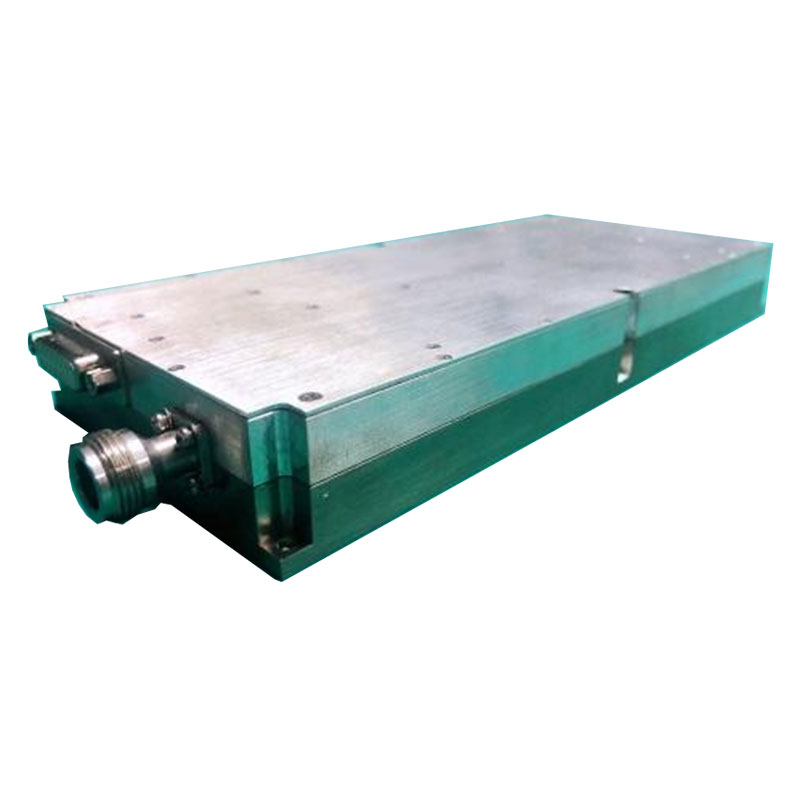

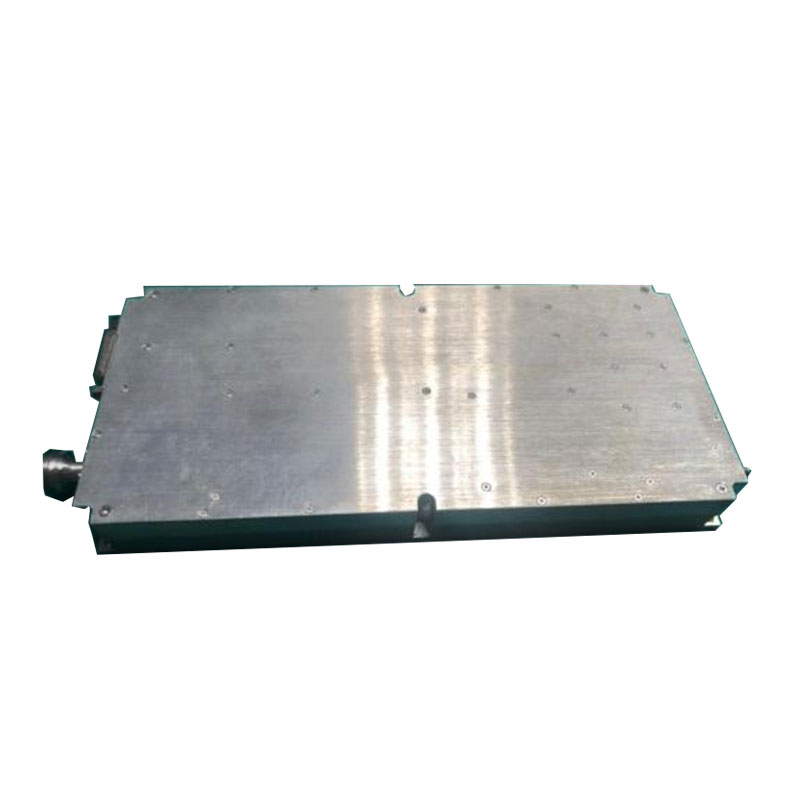

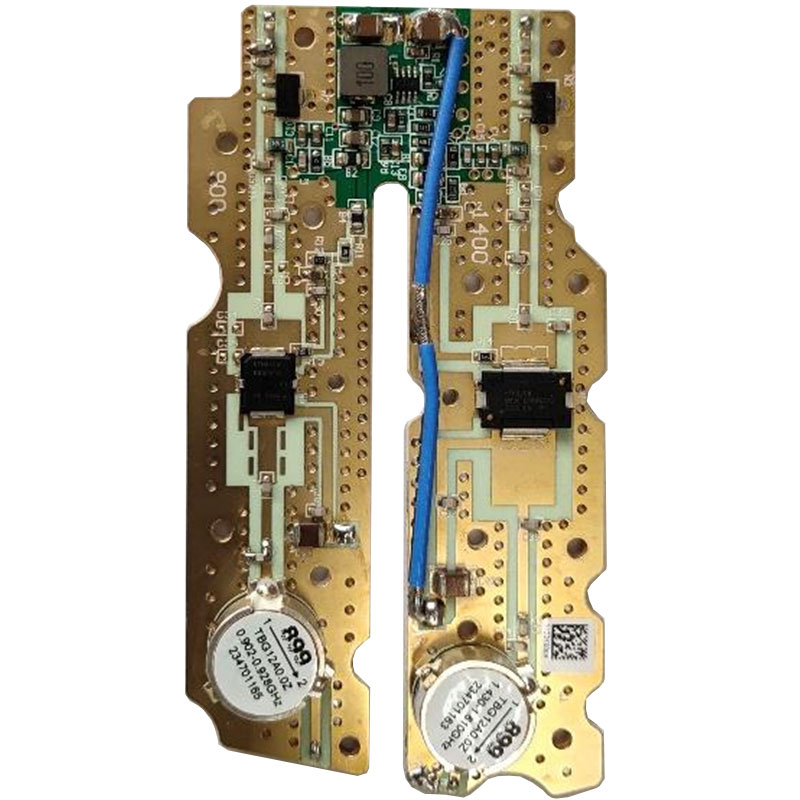

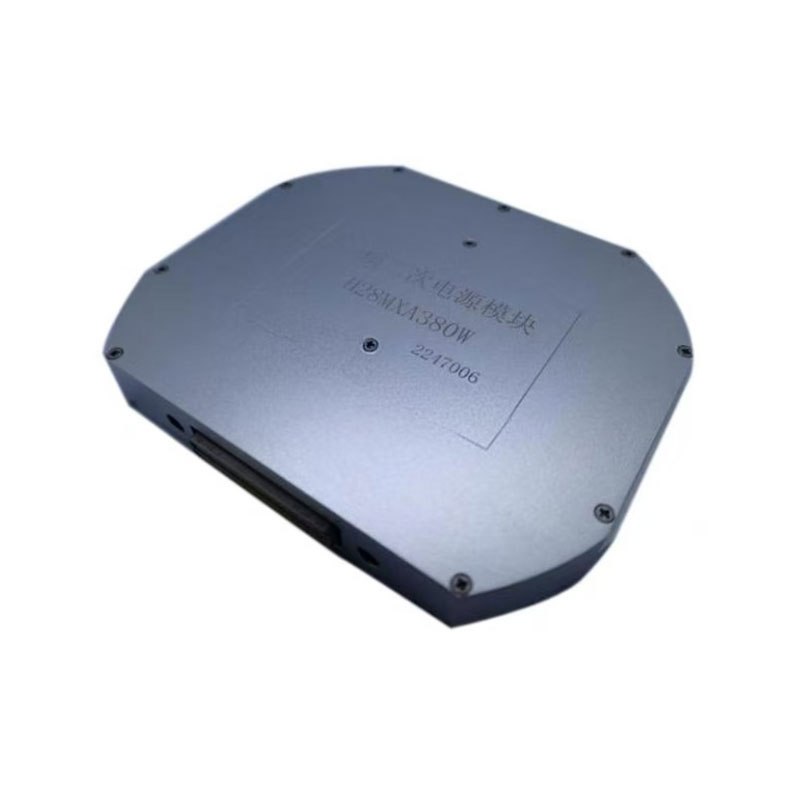

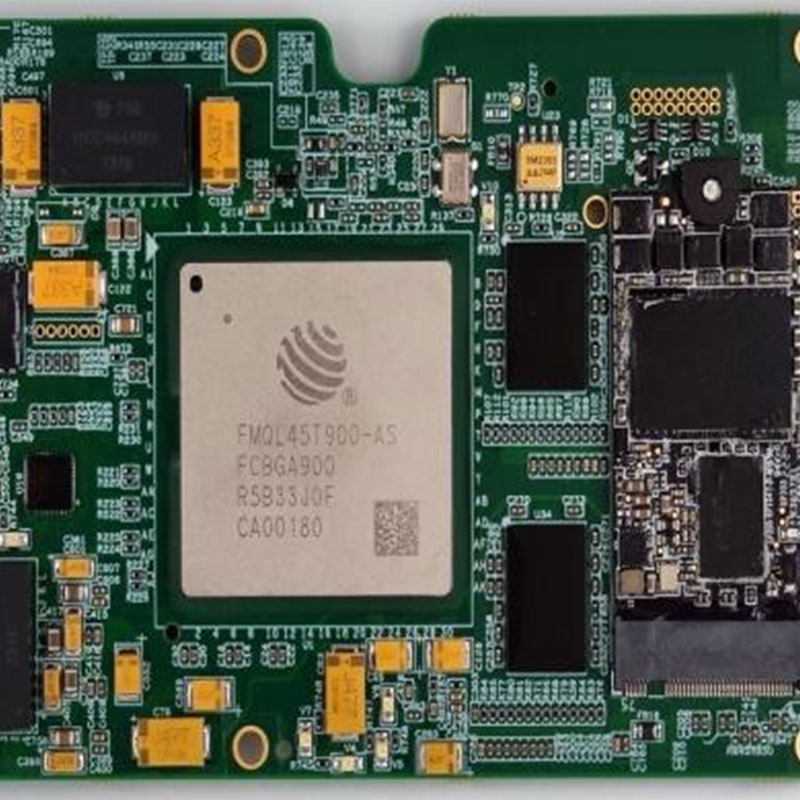

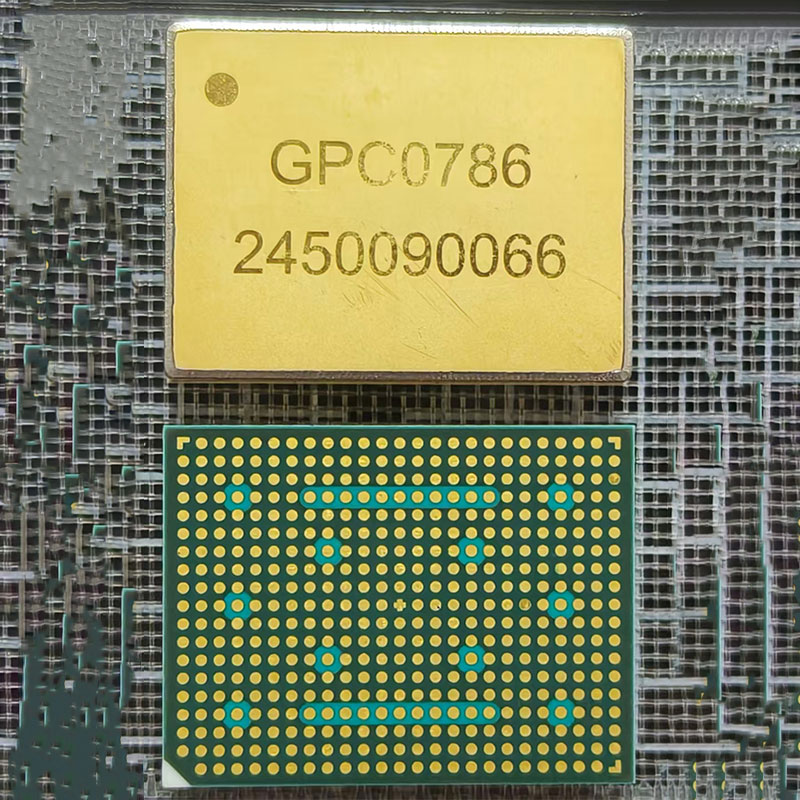

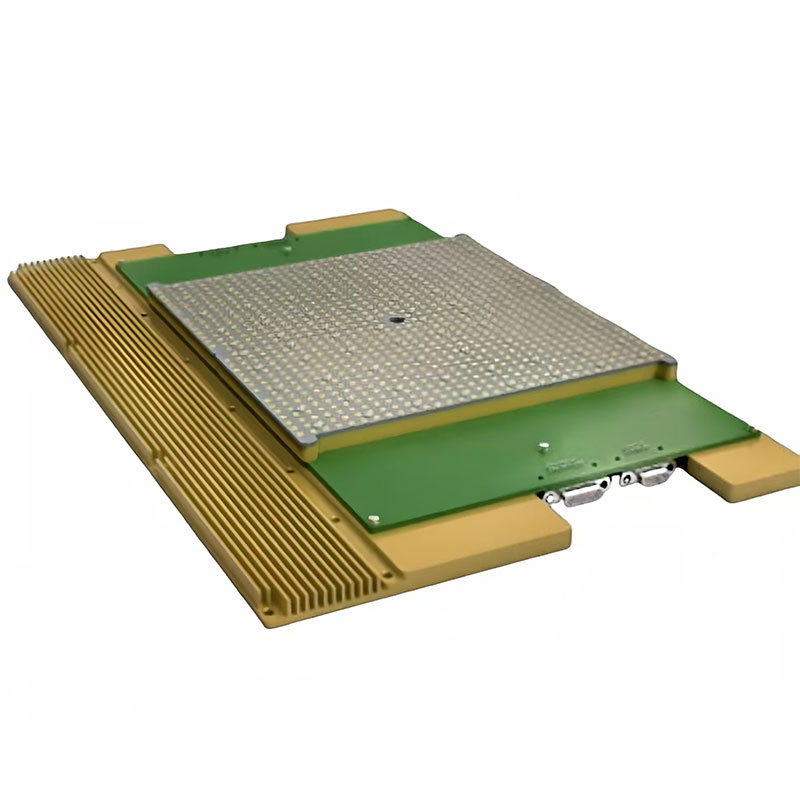

CWQ2P50

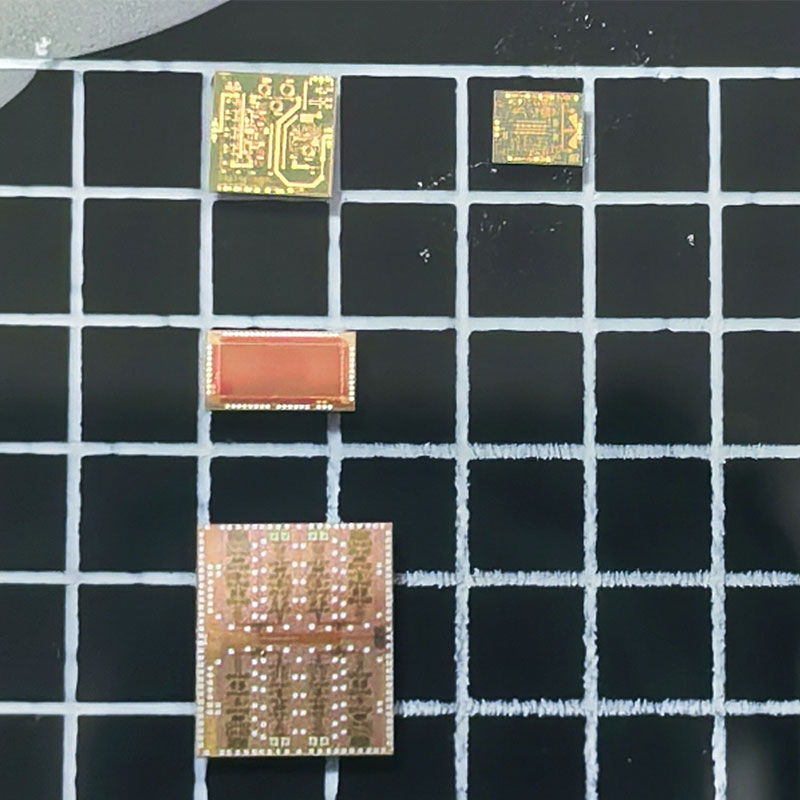

Технологический процесс: 28 нм, логические блоки: 52 КБ (адаптивная архитектура LUT6), блоки DSP: 120 (каждый включает предварительный сумматор, умножитель 25×18, сумматор и накопитель).

Описание

маркер

Представление продукта

Технологический процесс: 28 нм, логические блоки: 52 КБ (адаптивная архитектура LUT6), блоки DSP: 120 (каждый включает предварительный сумматор, умножитель 25x18, сумматор и накопитель), распределенная оперативная память (МБ): 0,6, блочная оперативная память (МБ): 2,7, блоки управления тактовой частотой: 5 (каждый включает модуль управления тактовой частотой смешанного режима и модуль ФАПЧ), максимальное количество пользовательских портов ввода-вывода: 210/250, напряжение ядра (В): 0,9, корпус (мм x мм): CSG324 (15x15) / FGG484 (23x23), класс качества: промышленный / GJB7400N1