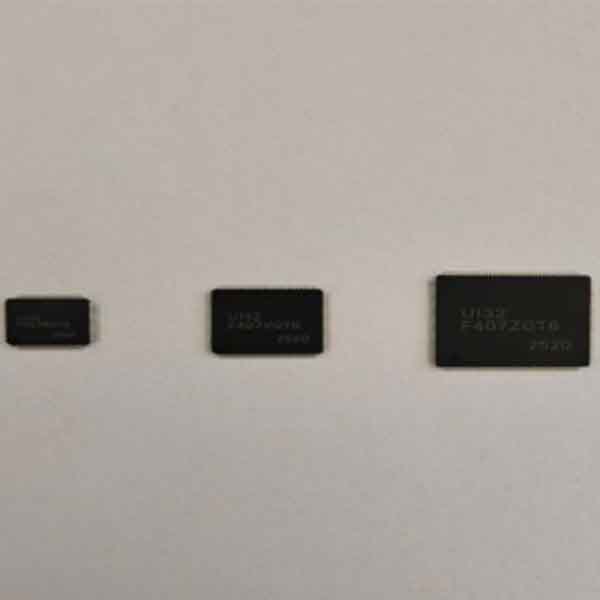

UI32E103xCxE

Ядро 32-битное ядро Arm® Cortex®-M3 Тактовая частота до 120 МГц Память и интерфейсы Flash: до 512 КБ SRAM: до 128 КБ EMMC: поддержка CF-карт, SRAM, PSRAM, SDRAM, NORи NANDпамяти

UI32F407xExG

Ядро 32-битное ядро Arm® Cortex®-M4Fс блоком FPU Максимальная тактовая частота: 168 МГц Память и интерфейсы Flash: до 1 МБ SRAM: системная память — 192 КБ, резервная — 4 КБ EMMC: поддержка CF-карт, SRAM, PSRAM, SDRAM, NOR и NAND памяти

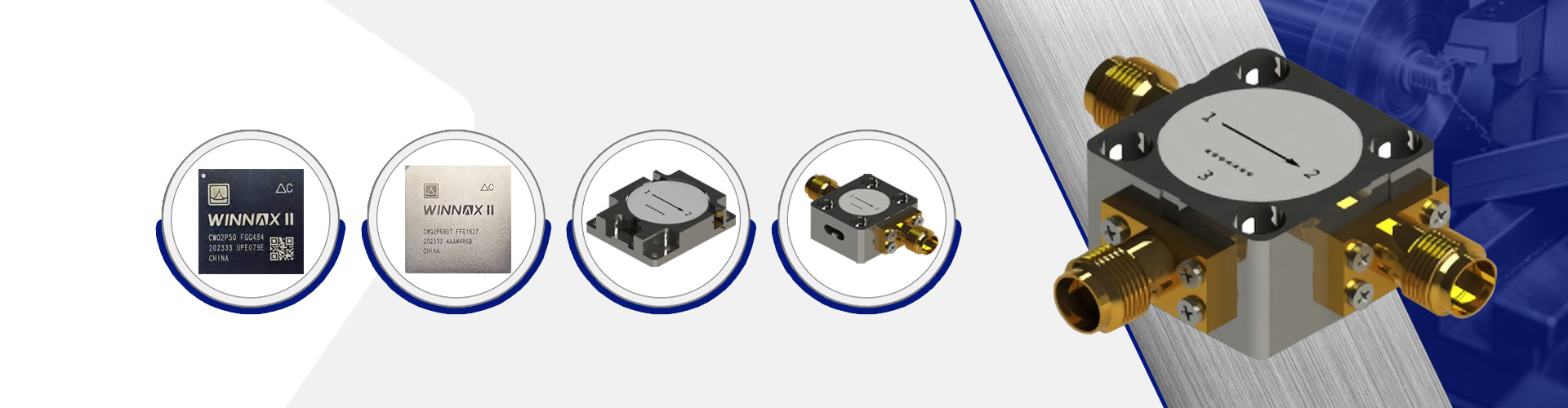

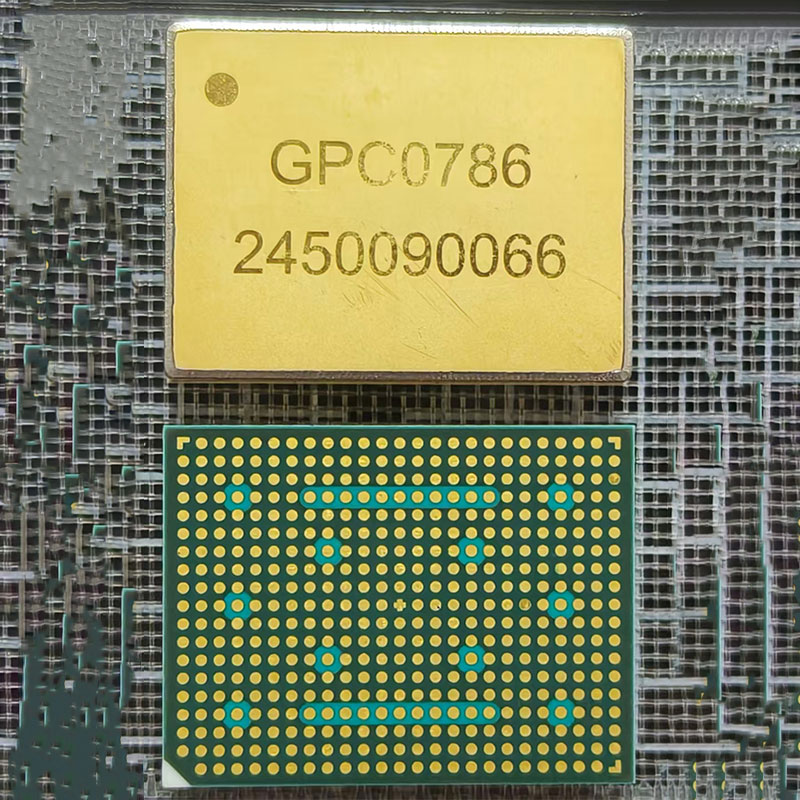

CWQ2P100T

Модель продукта: CWQ2P100T Технологический процесс: 28 нм Количество логических элементов: 100K (адаптивная структура LUT6) Количество DSP-блоков: 240 (каждый включает один умножитель 25×18, один сумматор и один накопитель) Объем распределённой RAM: 1 Мбит Объем блочной RAM: 4.8 Мбит

CWQ2P325T

Модель изделия: CWQ2P325T Технологический процесс: 28 нм Количество логических ячеек: 326K (адаптивная структура LUT6) Количество DSP-блоков: 840 (каждый включает предварительный сумматор, умножитель 25×18, сумматор и аккумулятор) Объем распределённой памяти (Distributed RAM): 4 Мбит

YX110156-1216P43

Этот микросхемный усилитель мощности изготовлен на основе 0,25 мкм технологии GaN HEMT. Диапазон рабочих частот охватывает 1,2 ГГц – 1,6 ГГц, коэффициент усиления по мощности превышает 17 дБ, типичная насыщенная выходная мощность составляет 43 дБм, а типичный коэффициент добавленной мощности (PAE) — 60 %. Микросхема может работать как в импульсном, так и в непрерывном (CW) режиме. Заземление осуществляется через сквозные отверстия на обратной стороне кристалла. Типовое рабочее напряжение: Vd = +28 В, Vg = −2,6 В.

Интегральный усилитель средней мощности HEM080A

Широкий диапазон частот: 1,0–4,0 ГГц Выходная мощность (Po): 20 дБм Хорошее согласование по импедансу 50 Ω, удобен для каскадного подключения

Интегральный широкополосный усилитель HE380

Диапазон частот: 10–400 МГц Высокая эффективность, широкий динамический диапазон: 35 мА при выходной мощности 17 дБм (типичное значение) Активная схема смещения с температурной компенсацией

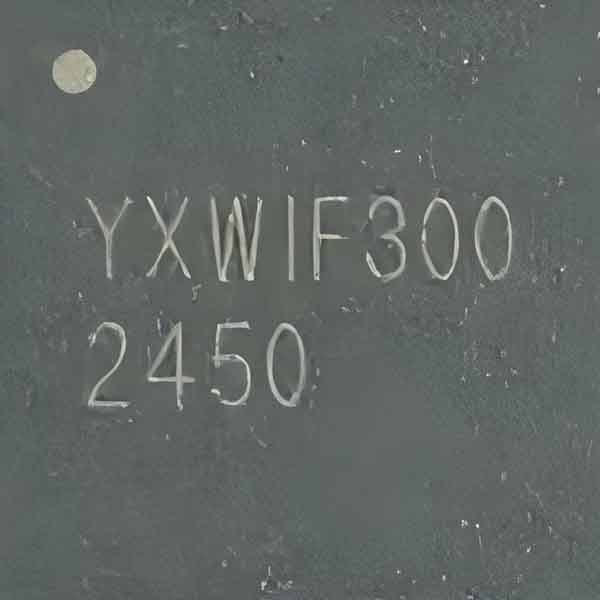

YXWIF300

YXWIF300 — это универсальная подсистема промежуточной частоты (ПЧ), предназначенная для цифровой обработки низкоуровневых входных сигналов в диапазоне частот 10–300 МГц с полосой пропускания 6,8–270 кГц.

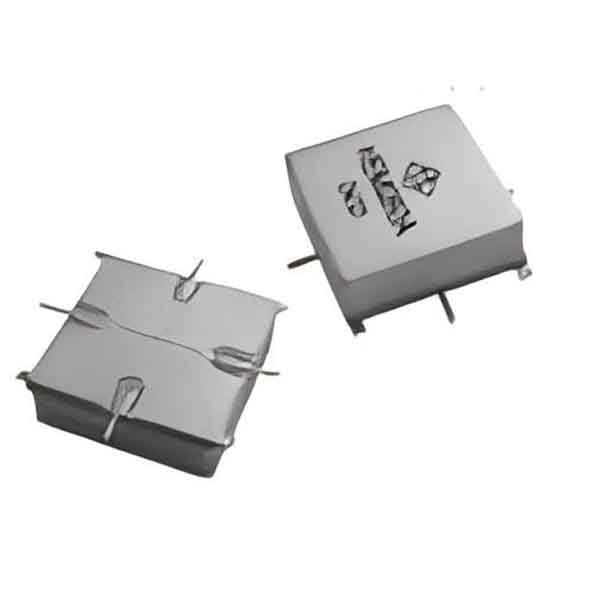

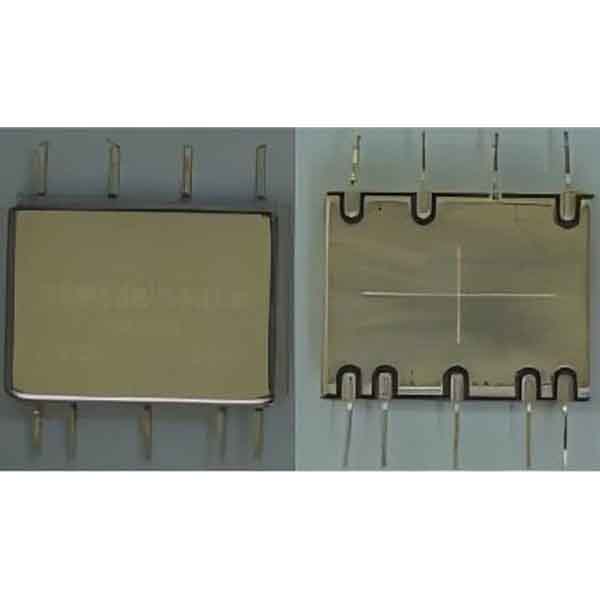

Двухкристальный кварцевый генератор серии TXM88 с температурной компенсацией и защитой от вибраций

Технологическая схема устройства основана на двойной кварцевой компенсации. Две кварцевые резонаторные пластины одновременно включаются в колебательный контур. Поскольку обе кварцевые пластины обладают одинаковой чувствительностью к ускорению, вызванные ускорением частотные флуктуации имеют одинаковую амплитуду, но противоположное направление, что позволяет значительно уменьшить частотные отклонения при вибрации.

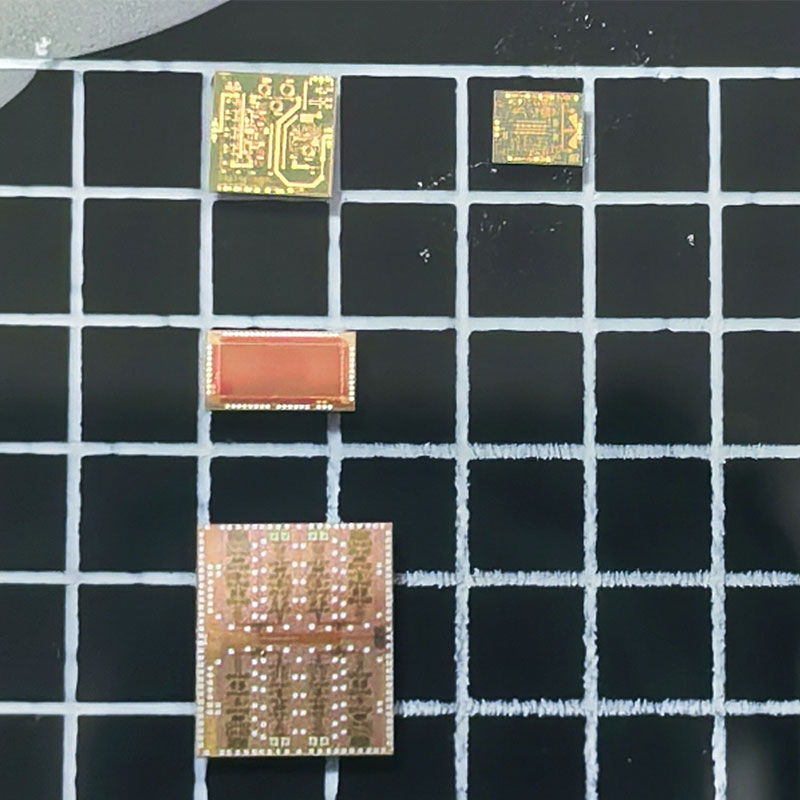

B коробка

SIP-модуль нижней частоты для K-диапазона, интегрирующий СВЧ-усилитель, СВЧ-фильтр, смеситель, цифровой аттенюатор, промежуточночастотный (IF) усилитель и фильтр, а также умножитель, усилитель и фильтр гетеродина. Модуль реализует усиление, фильтрацию и преобразование K-диапазонного сигнала в промежуточную частоту.

A коробка

Первый чип — это многофункциональный GaAs MMIC-чип с функциями связи, фильтрации и усиления. С помощью переключателей можно выбирать различные режимы входного сигнала, а также осуществлять его фильтрацию и усиление.

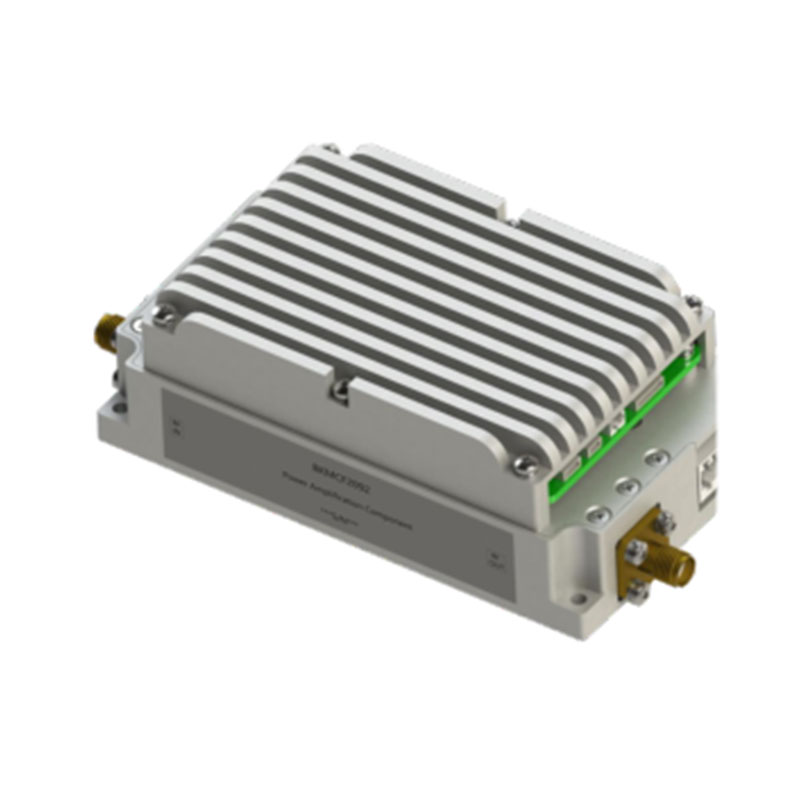

Компонент передачи сигнала

Данный компонент передачи силовых сигналов включает модуль передачи сигналов и модуль усиления мощности. Модуль передачи сигналов способен генерировать сигналы, а модуль усиления мощности усиливает эти сигналы. Компонент может передавать сигналы без отдельного источника сигнала.

Продукция

ООО Шицзячжуан Чжунчжичуансинь Технологии было основана в сентябре 2025 года. Компания может похвастаться командой с обширным практическим опытом, надежными техническими возможностями и приверженностью приоритету послепродажного обслуживания.