M28S5C25X

Диапазон входного постоянного напряжения: 4,9–5,1 В Выходной постоянный ток: 1,5 А Вход и выход изолированы от корпуса

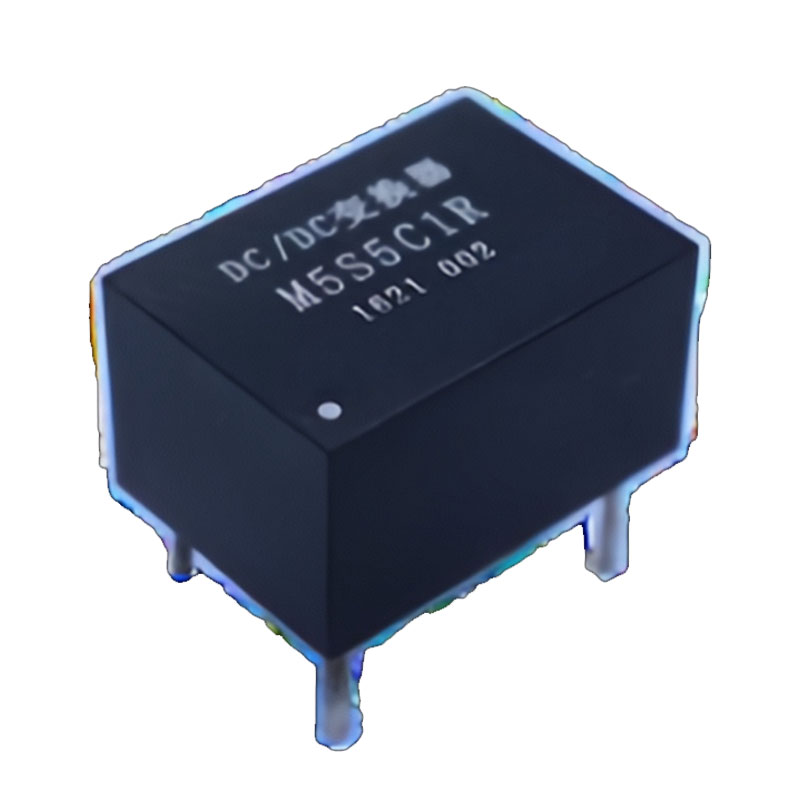

M5S5C1R

Диапазон входного постоянного напряжения: от 4,75 до 5,25 В Цельнометаллический корпус со всех шести сторон обеспечивает повышенную электромагнитную совместимость Высокая устойчивость к ударам и вибрации

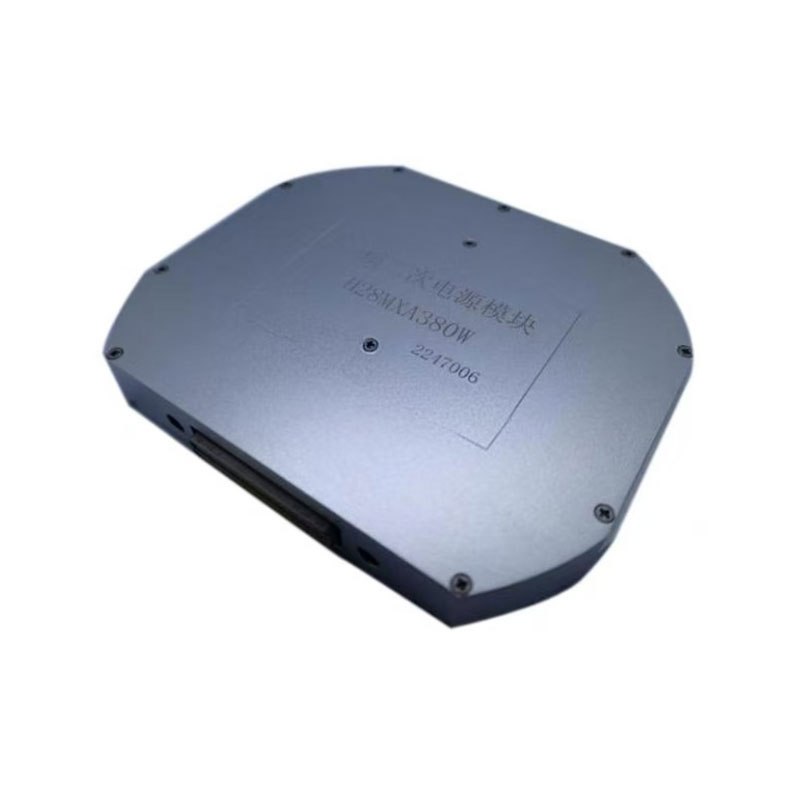

H28MXA380W

Восемь выходов постоянного тока, выходная мощность до 380 Вт Защита от короткого замыкания, перенапряжения и пониженного напряжения Вход и выход изолированы от корпуса

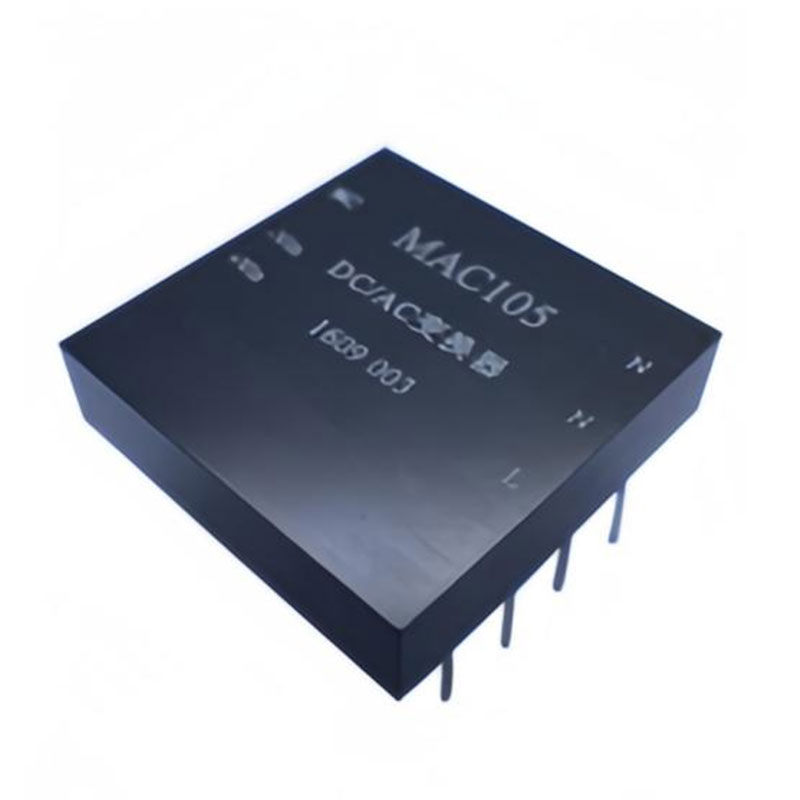

Силовой модуль M12S100AIR-GC

AID: Трехфазный или однофазный преобразователь переменного тока в постоянный; DID: Преобразователь постоянного тока в постоянный; AIA: Однофазный преобразователь переменного тока в переменный (с переменной частотой); DIA: Преобразователь постоянного тока в переменный (инвертор).

Модуль H28S5H25HF

В H28S5H25HF используется схема с несимметричной широтно-импульсной модуляцией, оптронная развязка и двойная замкнутая цепь напряжения и тока. Он обеспечивает стабильный выходной сигнал, минимальный температурный дрейф, высокую динамику и надёжную нагрузочную способность. Максимальная выходная мощность составляет 25 Вт.

VI1200F280S28TSPL 245-380 В Цельный кирпич

Защита от перегрузки по току, короткого замыкания и перенапряжения на выходе, защита от пониженного входного напряжения и защита от перегрева

VI600H28S28TNLB-G

Защита: защита от пониженного входного напряжения, защита от перегрузки по току/короткого замыкания/перенапряжения на выходе, защита от перегрева

M.2 PCIe

Поддержка программной/аппаратной защиты и защиты от отключения питания Поддержка механизма коррекции ошибок LDPC третьего поколения Поддержка сборки мусора, управления поврежденными блоками и выравнивания износа

U.2 PCIe

Поддержка программной/аппаратной защиты и защиты от отключения питания Поддержка механизма коррекции ошибок LDPC третьего поколения Поддержка сборки мусора, управления поврежденными блоками и выравнивания износа

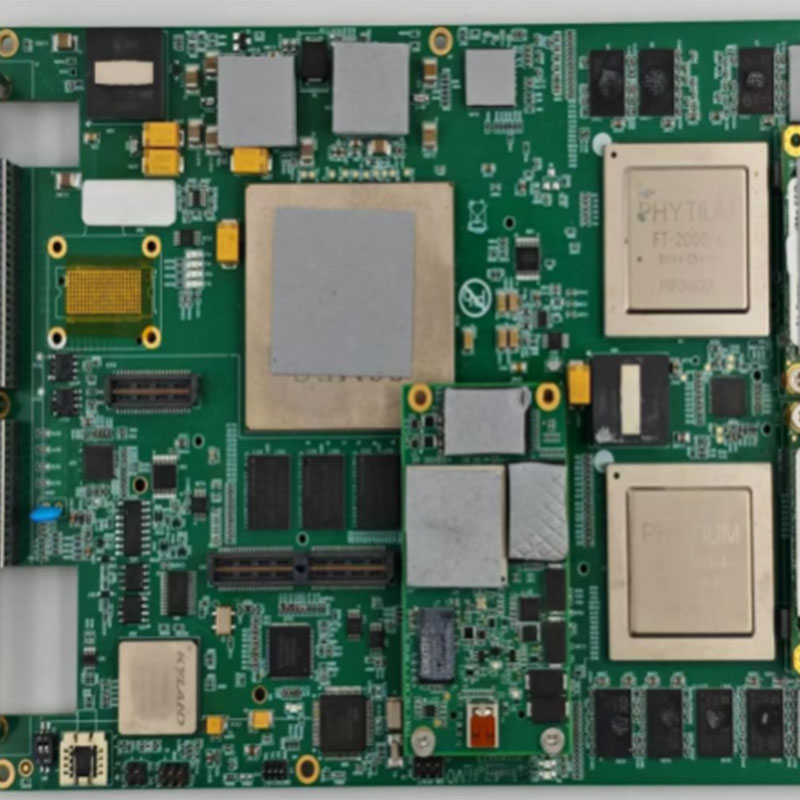

Многоканальный вычислительный модуль LRM

Универсальный вычислительный модуль, разработанный на основе стандарта ASAAC (часть 4), с четырёхъядерным процессором Feiteng FT-2000, мостовой микросхемой X100 и ПЛИС серии Guowei V7 в качестве основного процессора.

Модуль цифровой обработки

Модуль цифровой демодуляции и идентификации сигналов выполняет предварительную обработку цифровых сигналов, анализ сигналов связи и специальную обработку сигналов.

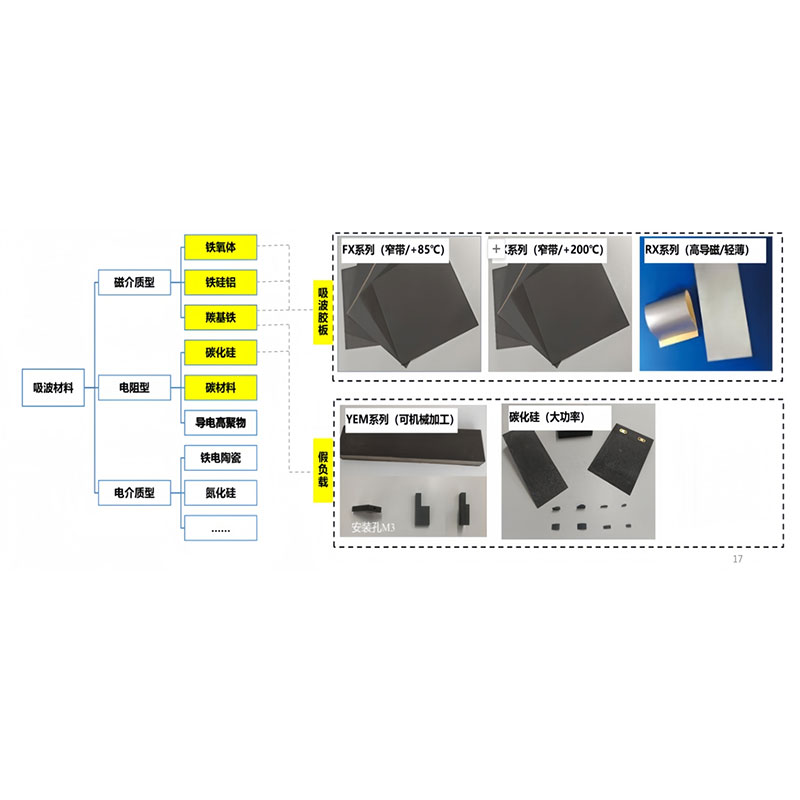

Радиопоглощающий материал

Поглощающие материалы — это тип композитного материала, способного поглощать или ослаблять энергию падающих электромагнитных волн.

Продукция

ООО Шицзячжуан Чжунчжичуансинь Технологии было основана в сентябре 2025 года. Компания может похвастаться командой с обширным практическим опытом, надежными техническими возможностями и приверженностью приоритету послепродажного обслуживания.